# dEsign enVironmEnt foR Extreme-Scale big data analyTics on heterogeneous platforms

## D3.2 — Data management techniques: final version

The EVEREST project has received funding from the European Union's Horizon 2020 Research & Innovation programme under grant agreement No 957269

#### **Project Summary Information**

| Project Title           | dEsign enVironmEnt foR Extreme-Scale big data analyTics on heterogeneous platforms |  |  |  |  |

|-------------------------|------------------------------------------------------------------------------------|--|--|--|--|

| Project Acronym         | EVEREST                                                                            |  |  |  |  |

| Project No.             | 957269                                                                             |  |  |  |  |

| Start Date              | 01/10/2020                                                                         |  |  |  |  |

| <b>Project Duration</b> | 42 months                                                                          |  |  |  |  |

| <b>Project Website</b>  | http://www.everest-h2020.eu                                                        |  |  |  |  |

## Copyright

© Copyright by the EVEREST consortium, 2020.

This document contains material that is copyright of EVEREST consortium members and the European Commission, and may not be reproduced or copied without permission.

| Num.       | Partner Name                                                          | Short Name | Country |

|------------|-----------------------------------------------------------------------|------------|---------|

| 1 (Coord.) | IBM RESEARCH GMBH                                                     | IBM        | CH      |

| 2          | POLITECNICO DI MILANO                                                 | PDM        | IT      |

| 3          | UNIVERSITÀ DELLA SVIZZERA ITALIANA                                    | USI        | CH      |

| 4          | TECHNISCHE UNIVERSITAET DRESDEN                                       | TUD        | DE      |

| 5          | Centro Internazionale in Monitoraggio Ambientale -<br>Fondazione CIMA | CIMA       | IT      |

| 6          | IT4Innovations, VSB – Technical University of Ostrava                 | IT4I       | CZ      |

| 7          | VIRTUAL OPEN SYSTEMS SAS                                              | VOS        | FR      |

| 8          | DUFERCO ENERGIA SPA                                                   | DUF        | IT      |

| 9          | NUMTECH                                                               | NUM        | FR      |

| 10         | SYGIC AS                                                              | SYG        | SK      |

Project Coordinator: Christoph Hagleitner – IBM Research – Zurich Research Laboratory

Scientific Coordinator: Christian Pilato – Politecnico di Milano

The technology disclosed herein may be protected by one or more patents, copyrights, trademarks and/or trade secrets owned by or licensed to EVEREST partners. The partners reserve all rights with respect to such technology and related materials. Any use of the protected technology and related material beyond the terms of the License without the prior written consent of EVEREST is prohibited.

#### **Disclaimer**

The content of the publication herein is the sole responsibility of the publishers and it does not necessarily represent the views expressed by the European Commission or its services. Except as otherwise expressly provided, the information in this document is provided by EVEREST members "as is" without warranty of any kind, expressed, implied or statutory, including but not limited to any implied warranties of merchantability, fitness for a particular purpose and no infringement of third party's rights. EVEREST shall not be liable for any direct, indirect, incidental, special or consequential damages of any kind or nature whatsoever (including, without limitation, any damages arising from loss of use or lost business, revenue, profits, data or goodwill) arising in connection with any infringement claims by third parties or the specification, whether in an action in contract, tort, strict liability, negligence, or any other theory, even if advised of the possibility of such damages.

#### **Deliverable Information**

| Work-package               | WP3                                       |

|----------------------------|-------------------------------------------|

| Deliverable No.            | D3.2                                      |

| Deliverable Title          | Data management techniques: final version |

| Lead Beneficiary           | USI                                       |

| Type of Deliverable        | Report                                    |

| <b>Dissemination Level</b> | Public                                    |

| Due Date                   | 31/01/2024                                |

#### **Document Information**

| <b>Delivery Date</b> | 27/06/2024                                                                                                                                                                                                                                                                                 |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| No. pages            | 46                                                                                                                                                                                                                                                                                         |

| Version   Status     | 1.1   Revised                                                                                                                                                                                                                                                                              |

| Responsible Person   | Francesco Regazzoni (USI)                                                                                                                                                                                                                                                                  |

| Authors              | Francesco Regazzoni, Tom Slooff, Subhadeep Banik, Alberto Ferrante (USI), Jan Martinovic, Jakub Beranek, Katerina Slaninova (IT4I), Karl Friebel, Jeronimo Castrillon (TUD), Serena Cruzel, Christian Pilato (PDM), Michele Paolino, Samuele Paone (VOS), Burkhard Johannes Ringlein (IBM) |

| Internal Reviewer    | Christoph Hagleitner (IBM)                                                                                                                                                                                                                                                                 |

The list of authors reflects the major contributors to the activity described in the document. All EVEREST partners have agreed to the full publication of this document. The list of authors does not imply any claim of ownership on the Intellectual Properties described in this document.

### **Revision History**

| Date       | Ver.                                                                           | Author(s)                                  | Summary of main changes              |  |  |  |  |

|------------|--------------------------------------------------------------------------------|--------------------------------------------|--------------------------------------|--|--|--|--|

| 13.10.2023 | 0.1                                                                            | Tom Slooff (USI)                           | Initial draft                        |  |  |  |  |

| 3.12.2023  | 0.2                                                                            | Tom Slooff (USI)                           | Updated Anomaly Detection            |  |  |  |  |

| 13.1.2024  | 0.3                                                                            | Michele Paolino and<br>Samuele Paone (VOS) | Updated Virtualization               |  |  |  |  |

| 9.02.2024  | 0.4                                                                            | Burkhard Ringlein (IBM)                    | Updated Cloud FPGA communication     |  |  |  |  |

| 28.02.2024 | 0.5                                                                            | Serena Cruzel (PDM)                        | Updated Custom Data Type             |  |  |  |  |

| 28.02.2024 | 0.6                                                                            | Subhadeep Banik<br>(USI)                   | Added Security Library               |  |  |  |  |

| 7.03.2024  | Jan Martinovic and                                                             |                                            | Updated Data Management Architecture |  |  |  |  |

| 15.03.2023 | 5.03.2023  O.7 Francesco Regazzoni Alberto Ferrante (USI) Christoph Hagleitner |                                            | Assembly                             |  |  |  |  |

| 23.03.2024 |                                                                                |                                            | Review                               |  |  |  |  |

| 26.03.2024 | 1.0                                                                            | Christoph Hagleitner (IBM)                 | Final                                |  |  |  |  |

| Date       | Ver. | Author(s)                                                                                                                                            | Summary of main changes |

|------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| 26.06.2024 | 1.1  | Francesco Regazzoni<br>Tom Slooff (USI)<br>Michele Paolino (VOS)<br>Jan Martinovic (IT4I)<br>Christian Pilato (PDM)<br>Christoph Hagleitner<br>(IBM) | Revision                |

## **Quality Control**

| Approved by Internal Reviewer      | March 25, 2024 |

|------------------------------------|----------------|

| Approved by WP Leader              | (N.A.)         |

| Approved by Scientific Coordinator | March 26, 2024 |

| Approved by Project Coordinator    | March 26, 2024 |

## **Table of Contents**

| 1  | EXECUTIVE SUMMARY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 6                                                                                |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| 2  | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 7                                                                                |

|    | DATA MANAGEMENT TECHNIQUES  3.1 Data Allocation and Storage  3.1.1 Memory-related optimizations  3.1.2 Storage of Data at Cluster Level  3.2 Data Processing and Communication  3.2.1 VMs guests-host (PCle virtualization) communication extensions  3.2.2 Data management techniques for the cloudFPGA platform  3.2.3 Data management techniques for Xilinx Alveo accelerators  3.2.4 HLS data management techniques  3.2.5 Inter-Node and Inter-Cluster communication  3.3 Data Protection  3.3.1 Anomaly Detection  3.4 Cryptographic Libraries for Data Protection  3.5 Architectures  3.5.1 Cryptographic Primitives: Block Ciphers  3.5.2 Cryptographic Primitives: Stream Ciphers  3.5.3 Cryptographic Primitives: Authenticated Encryption | 11<br>12<br>12<br>13<br>13<br>15<br>17<br>26<br>27<br>29<br>30<br>30<br>31<br>33 |

| 4  | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 41                                                                               |

| Ri | EFERENCES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 43                                                                               |

## **1 Executive Summary**

This deliverable reports the final version of the Data Management Techniques (DMTs) studied, developed, and adopted within the EVEREST project. It depicts the definition of techniques related to data layout, communication, and security. This deliverable is an updated version of Deliverable D3.1 "Data management techniques: initial version", and extends this initial version of the DMTs by presenting the optimization, the changes, and the novel techniques that have been developed in the second part of the project. Since our goal is to provide a self contained document that does not require prior knowledge of the content of Deliverable D3.1 to be completely understood. While preparing this deliverable we followed an incremental approach. This means that we started the current deliverable from the text, the figures, and the tables that were already part of Deliverable D3.1. We updated content in this deliverable where needed, but left it unchanged where it was still valid. Next, we added new sections, figures and tables to describe the new results and methods developed in the second part of the project.

We followed the same structure of Deliverable D3.1, describing firstly the general position of the DMTs within the EVEREST data-lifetime explaining the difference between the data management techniques describe in this deliverable and the initial data management plan described in D1.3. Then we present, at high level, the final version of the EVEREST data management architecture, which has been updated compared to Deliverable D3.1. Finally, we summarize the efforts done throughout the project discussing the DMTs developed for the FPGA memory architecture, for data allocation and storage, for the FPGA data processing, for virtualization, for custom data types and for providing data protection via anomaly detection and via a library of cryptographic primitives.

#### 2 Introduction

This deliverable presents the final version of the DMTs, whose initial version was provided in deliverable D3.1. The goal of the EVEREST project is to establish the convergence between big data and HPC, focusing on a data-centric perspective and considering software tools that go beyond the border of a single hardware platform. In this deliverable, we focus on the DMTs that deal with the data needed for the execution of an EVEREST workflow.

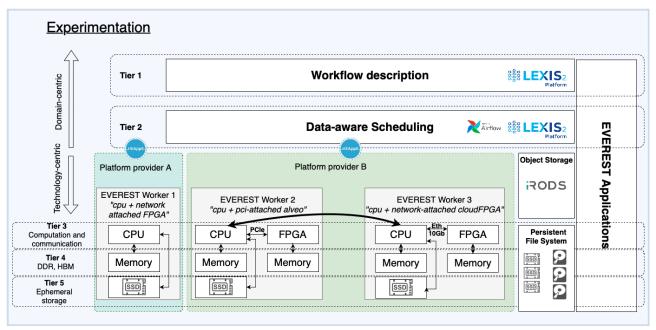

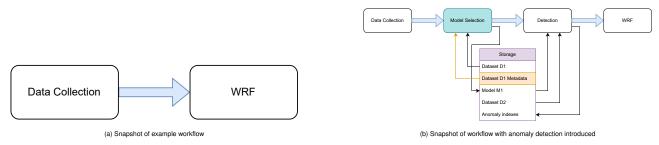

The initial high level vision of the Data Management Architecture has been refined throughout the course of the project. The updated version of the architecture is depicted in Figure 1. We can see the categorization of the data management process into five tiers. The data management requirements of each tier are addressed by different tools and technologies suitable for the purpose.

Figure 1 – The EVEREST Data Management Architecture (EDMA)

The first tier is used for the definition of the EVEREST high-level application complex workflows. Tasks in these workflows are already deployed HPC applications, containerized applications, data movement operations, etc. The workflows on this tier are represented by directed acyclic graphs (DAG) implemented in Python and orchestrated by the Apache Airflow [6] using custom operators implemented as a comprehensive library which is part of the LEXIS Platform [38, 39].

The LEXIS Platform implements the concept of a workflow, which executes a particular DAG. This execution accepts a set of input parameters, and the individual tasks are triggered according to their dependencies defined in the DAG file. In the second tier, Apache Airflow ensures the correct ordering of task executions, which triggers appropriate APIs for asynchronous data and HPC job management (using HEAppE middleware [37]) and implements a mechanism for observing state changes of the operations.

The third tier includes the data management within the tightly coupled processing units of the EVEREST platform, i.e., CPUs and FPGAs (PCle-attached and network-attached). The fourth tier includes the data management at the boundaries of the processing elements and the external fast memory, i.e., Double Data Rate (DDR) and High Bandwidth Memory (HBM). The fifth tier includes the data management at an optional ephemeral SSD-based storage within the boundaries of an EVEREST node.

Persistent storage is provided by persistent file systems or by object stores of the LEXIS Platform Distributed Data Interface (see Section 3.1.2). As it can be seen, EVEREST applications span over all the tiers. This architecture offers to users of EVEREST the possibility to develop applications in a way that is transparent to the actual physical platform where the workflow will be executed.

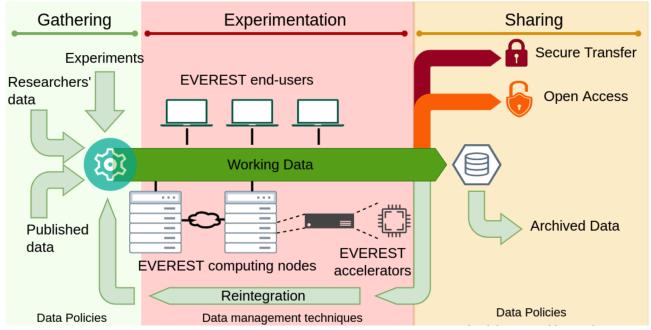

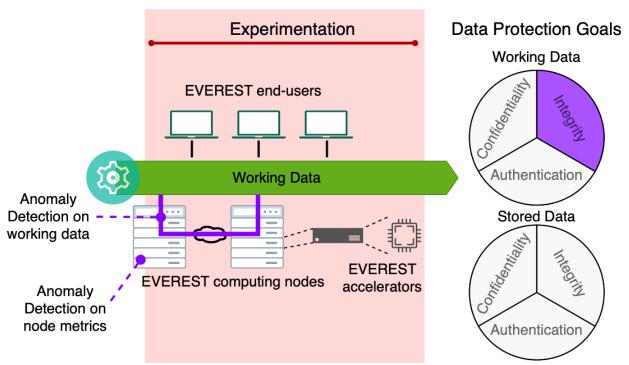

In the remaining part of this section, we recall the whole EVEREST data-lifetime cycle, which is depicted in

Figure 2. The figure reports three main categories for the EVEREST Data Lifetime:

- Data gathering: The process of collecting data from various sources to process in the following stage.

- Experimentation: The main process of performing calculation on data to derive useful insights for the EVEREST applications.

- Data sharing: The process of offering the results of the previous stage to other interested parties, either in a confidential, open-access policy or as an input to the gathering stage in the form of a feedback loop (reintegration).

Using the categories identified in the figure, the activities presented in this deliverable are positioned mostly on the data during the experimentation phase.

Figure 2 – The EVEREST data-lifetime, data gathering and sharing are mostly covered in deliverable D1.4, this deliverable D3.2 addresses the data management techniques used for experimentation.

## 3 Data Management Techniques

The DMTs reported in this section describe the methodologies and tools that have been developed and used during the whole EVEREST project. Several techniques envisioned, used, and developed in the first part of the project and described in Deliverable D3.1 have been maintained and confirmed also in the second part of the project, thus their description remain unchanged.

A key enabler for DMTs within the EVEREST project is the use of domain-specific programming abstractions. These programming abstractions convey information to the compilation and optimization flow about data-centric operations. To support the different use cases, we developed and leveraged abstractions for data structures (e.g., tensors in CFDlang and Machine Learning), for known operators (e.g., tensor contractions, stencils and convolutions), and for explicit typed data communication in the Ohua dataflow programming model. These data abstractions ensure a seamless integration in the high-level transformations and in the code generator. More concretely,

- Data structures: With index-free DSLs, the compiler has full control on the data layout and materialization

of multi-dimensional arrays. This allows for high-level data partitioning, for advanced polyhedral analysis

and scheduling, and for buffering optimizations. Via annotations, the user can specify custom data types,

further reducing the memory footprint of data structures and allowing for trade-off exploration between

memory bandwidth and area in the reconfigurable fabric.

- Known operators: With explicit syntax for operators, the compiler has rich information about memory access patterns. We thus capture high-level stencils, tensor operators and machine learning kernels. By abstractly specifying a stencil, the compiler can decide on the interplay between data allocation, buffering, re-computation and stencil scheduling. With known tensor operators, like contraction or tensor products, the compiler can decide on the most suitable implementation via algebraic transformations (e.g., sequence of transpositions followed by matrix-matrix multiplication). By capturing the structure of a deep neural network, the compilation flow can decide on how to implement ML engines in the reconfigurable hardware (e.g., streaming or batching).

- Dataflow: Typed dataflow channels, makes it easier to offload computation to accelerated kernels in FPGAs. This includes transparent data marshalling.

These data-centric abstractions are accessible through DSLs and are represented within the EVEREST compiler with suitable intermediate representations (see Deliverable D4.2 and Deliverable D4.5). Compared to what we reported in Deliverable D3.1, extensions to the programming abstractions to provide better control on data abstraction are: (1) a complete Einstein Summation Notation for tensor expressions, and (2) a formal abstraction of dataflow with explicit control of accesses (read and write) to data channels. The former includes support for indirect accesses via subscripts of subscripts, which provide better control on data access patterns. The latter enable better type-safe analysis as enabler for the memory-related optimizations mentioned below.

## 3.1 Data Allocation and Storage

In EVEREST, we apply several memory-related optimizations to reduce the resource requirements (to possibly fit in more parallel computational units) or to facilitate optimizations of the computational part.

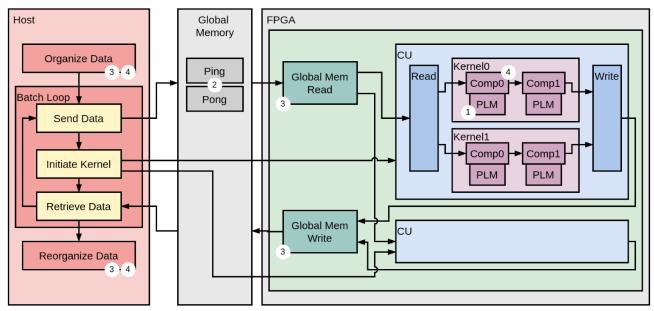

Figure 3 shows the hardware architecture common to the accelerators generated by the EVEREST SDK. In the FPGA side, a computational unit (CU)<sup>1</sup> is replicated one or more times based on the available logic resources and memory channels.

To optimize the use of on-chip memories (1), we apply **memory sharing** to reduce the Block Random Access Memory (BRAM) requirements of each kernel generated with HLS. To this end, we exploit the information on the data and the interfaces computed by the compiler during liveness analysis. Based on this, it applies

<sup>&</sup>lt;sup>1</sup>We use the Xilinx terminology of "Computational Unit" to refer to the largest unit of computation that can be generated by the compilation flow and possibly replicated into the final hardware architecture to parallelize data processing.

Figure 3 - FPGA memory architectures of the EVEREST accelerators.

sharing transformations based on a memory compatibility graph, which we can easily compute from the compiler for any given schedule. Our memory generation flow then uses this information to generate **zero-conflict memory architectures** while guaranteeing fixed latency of the memory accesses. It can also create multi-port, multi-bank architectures based on the requested HLS optimizations. In this way, the HLS tool can compute a more efficient scheduling of the computational part.

Our hardware generation flow aims at optimizing the data transfers around the kernel implementation produced by the compiler flow. In particular, EVEREST aims at generating hardware accelerators and the associated memory architectures like the one shown in Figure 3.

In this phase, we apply different optimizations on the data allocation to facilitate hardware execution, such as:

- Double buffering: To overlap the host-FPGA data transfers with the execution of the hardware module, we use **double buffering (2)** that requires the allocation of consecutive data chucks to different memory regions that can be transmitted independently.

- Memory layout reorganization: In the case of large bus lines (e.g., the 256-bit Advanced eXtensible Interface (AXI) interfaces of the PCIe-attached memory architectures) or custom data types with reduced bitwidths, EVEREST uses bandwidth optimization (3) methods to better exploit the available bandwidth and reduce the number of clock cycles for data transfers. To fully exploit the parallelism, we conceptually divide the bus into smaller and parallel lanes that can be accessed independently by the parallel kernels. Algorithms for better data layouts have been also proposed to maximize the bandwidth utilization. To obtain this layout, the host code data allocation must be modified to interleave the input for the multiple elements before sending it to the FPGA and de-interleave the output after receiving the results.

- Custom precision floating-point: Where full precision is not required power consumption and datatransfer/computation latency can benefit from the use of **smaller bitwidth floating-point types (4)**, while preserving results' precision.

All these optimizations affect the allocation of data in memory and so are implemented in the customization of the host functions (see Deliverable D4.4 for more details). These optimizations apply to the use of the on-chip memories and the data layout in off-chip memories.

For the memory aspects of a hardware accelerator, EVEREST proposes an approach based on a **memory template** that allows for the specialization of the components. The template comprises existing memory primitives, like caches, Direct Memory Access (DMA) engines, prefetchers, and private-local memories (multiport on-chip memories with fixed-latency access). Based on given area constraints, only part of the data can D3.2 - Data management techniques: final version

stay on chip, while the rest is stored in DRAM (either on the same device or in another that can be accessed through via inter-node data transfers). On-chip data are stored in different memories based on the application data structures but also the type of accesses that are expected. Irregular accesses are implemented with custom **latency-insensitive memory architectures** [47].

Data with regular accesses can be stored in fixed-latency **private local memories** (PLMs) and customized with multi-bank configurations to expose many ports to the accelerator logic. Data reuse buffers can remove unnecessary data transfers. Data accesses with a certain degree of locality can benefit from architectures featuring **caches** that are local or shared with the processor by means of a coherent protocol. We also feature a **DMA engine** to make the data transfers more efficient and we can introduce **prefetchers** to anticipate known data transfers to hide the communication latency. These IP blocks can be also special functions that can include security modules (e.g., encryption/decryption engines) or application-specific transformations (e.g., synthesizable matrix transpose for near-data computing).

This template is general enough to be reused across many kernels, but it can also be specialized based on the accelerator characteristics. For instance, we can vary the number of ports on a multi-bank memory based on the specific access patterns of the given application kernels. Also, components can be removed if they are unnecessary. For example, if the data resides entirely on-chip, the prefetcher can be removed or if there is only a single memory, the multi-channel controller can be simplified. On the contrary, for both network-attached and PCIe-attached FPGAs, the support for multiple channels is important to exploit the bandwidth and supply the parallel execution of the hardware resources with enough data.

#### 3.1.1 Memory-related optimizations

In the following, we describe data optimizations that we include in EVEREST. Such optimizations can be extended to many big data applications that make large use of tensor operators.

On-Chip Memory Optimization. The tensor-based kernels can be often decomposed into a sequence of loops that are executed in sequence. Each loop produces a tensor. Intermediate tensors are used by the next loops. Each of these matrices requires on-chip resources (generally BRAM) to store the values. The number of available BRAMs can limit the number of FPGA kernels. However, once the matrix is not used anymore, the corresponding BRAM resources can be used by the same kernel to store new data. Using the liveness information generated by the compiler, we can reduce the number of on-chip resources required by each kernel. Indeed, arrays with disjoint lifetimes can use the same physical memory banks. Reducing the kernel's BRAM requirements can increase the total number of kernels that we can instantiate. However, sharing opportunities can operate only inside each subkernel. So, the effects of this optimization may be limited.

Host-FPGA Double Buffering. In a naive implementation, the host code transfers the data required for computation into the FPGA. The Compute Units (CU) are then called upon to execute on each of these elements and generate the corresponding output results. The host transfers these outputs back from HBM to its main memory. Each CU interfaces with one PC and we can instantiate up to 32 CUs (each with one kernel) to operate in parallel. However, all communication and execution for a single CUs are serialized. Since the host-HBM communication as much expensive as the computational part, this significantly affects the overall performance. To overlap the host-HBM data transfers with the CU execution, we use double buffering where each computational unit interfaces with two channels. When the total host transfer time for input and output of one batch is less than the total CU execution time for the same batch, the host transfer time is entirely hidden and the CUs are actively executing at all times.

**Bandwidth Optimization.** The data elements of an application do not usually require more than 64 bits, even less in case of custom data types. However, modern FPGA architectures feature wider busses so using only part of the bus line to transfer the data leads to underutilize the bandwidth. It is possible to "pack" more data elements to significantly reduce the number of clock cycles for data transfers. However, to do so, the CPU code must efficiently prepare the data in the FPGA memory or into the network packets and the accelerator needs to efficiently manage the multiple parallel data to avoid serialization when writing them into the buffers. To fully exploit the parallelism, we conceptually divide the bus into multiple lanes and replicate the innermost kernel as many times as needed within a CU, allowing each kernel to access one of the lanes. This way,

read/write modules still require the same number of cycles, but the accelerator can start the computation of more "hardware threads" in parallel. An additional optimization uses custom data layouts with scheduling principles for maximizing the bandwidth utilization [50].

**Dataflow Optimization.** Each single execution of the CU reads data from the FPGA memory, execute the kernel operator(s) on them, and write back the results. When the kernel can be decomposed into multiple operations, we can decompose the hardware module accordingly into elementary blocks. Such blocks can be implemented as subfunctions in the kernel that communicate via AXI Stream in a dataflow model. These hardware modules will thus execute in a pipeline, significantly improving the throughput. The number of elementary blocks in each subfunction is a tradeoff between latency and resource requirements. Indeed, having more blocks in the same subfunction increase resource sharing opportunities but also increases the latency of the pipeline stages, reducing the throughput. This optimization improves the performance but also increases the resource usage, potentially limiting the total number of CUs that can be instantiated.

**Custom floating-point types.** Given the nature of the application data, it is often possible to customize the bitwidth of the data without significant error degradation. From the memory viewpoint, data types with reduced bitwidth require less on-chip memory resources, reducing the number of BRAM units that can be used. Also, reducing the precision of the data allows for creating more "lanes" and thus enabling more parallel computation.

#### 3.1.2 Storage of Data at Cluster Level

Data on the cluster level at IT4I reference infrastructure are handled by the Distributed Data Interface (DDI) service which is part of the LEXIS Platform. The service provides asynchronous data transfers between geographically distant data sources such as federation of iRODS zones. The service uses remote worker processes implemented in Celery framework in Python. These worker processes use native client libraries to transfer the data, in case of the clusters it uses native SSH-based protocols for data transfers like sftp or rsync. It uses userspace level of access to the cluster and does not require any change in the cluster configuration. The credentials and preparation of a work directory are handled by the HEAppE middleware, which the worker process calls.

The DDI service provides REST API for data management, which resembles traditional object storage extended with rich metadata index. The API provides a set of user endpoints for direct data transfers using HTTPS based chunked upload (TUS protocol) and direct downloads. Another set of enpoints is provided to manage the asynchronous data transfers between external data sources and HPC clusters. The LEXIS Platform also offers a Python library Py4Lexis [40] which offers Python API as well as interactive terminal-based interface for all DDI features, including direct access to iRODS zones connected to the LEXIS Platform for large data transfers.

The DDI capabilities are nicely illustrated by their integration in the LEXIS workflows. The user first uses the DDI to upload their input data and metadata to a particular iRODS zone and then executes a workflow, where the uploaded input dataset is specified as paramater. The LEXIS workflow orchestrator then triggers data movement through the DDI, which issues a set of tasks for the worker process, which in turn pulls the data from the remote iRODS zone to a temporary staging area and uses HPC cluster native protocol to stage the data to the cluster. The orchestrator then triggers an HPC job submission through the HEAppE middleware. Once the job finishes, the orchestrator then triggers a DDI operation which transfers the output data produced by the HPC job and stores them as a dataset in a selected iRODS zone along with a set of metadata. These metadata also contain apart from user specified values also provenance metadata about the workflow and its execution used to produce the output dataset.

## 3.2 Data Processing and Communication

The scope of this subsection is to cover the activities related mainly with the data processing and communication. In this task we define how the different components interact with the memories and communicate with each other. Concerning data processing, this task will analyze the data access patterns, and the alignment of data accesses with the width of the memory, taking into consideration the different memories of the EVEREST

heterogeneous platform. Memory access are also optimized for virtualized environments by enhancing the performance of transactions between the virtual machines and the hardware accelerators, aiming at minimizing data processing latencies and increasing the guests-hardware bandwidth.

We start the description of those activities by firstly providing information about the virtualization technology of PCIe-attached FPGAs and afterwards on the DMT for the FPGA-based EVEREST heterogeneous platform.

#### 3.2.1 VMs guests-host (PCIe virtualization) communication extensions

EVEREST supports virtualization with a dedicated framework, the EVEREST Virtualization Framework, that is designed to simplify the use of FPGAs in virtual environments. As detailed in Deliverable D5.5, where the framework is presented in depth, it leverages the SR-IOV support of the Xilinx QDMA IP to automate the main actions related with accelerators associated with VMs, such as the creation, the attachment/detachment and reconfiguration, automate several operations with dedicated scripts, and provides a pause functionality to allow VFs reconfiguration without detaching from the guest. The virtualization framework functionalities (e.g., ESFM, QDMA manager, QEMU extensions) are developed in WP5 (and, because of that, a detailed description about such extensions and the EVEREST virtualization framework and its components can be found in Deliverable D5.5). The part related to the communication between guests and the host is developed in WP3. This part includes QDMA Virtual Function (VF) and Physical Function (PF) drivers extensions that are detailed here below.

In the Deliverable D3.1 we highlighted the "VMs guests-hosts data transfer optimization" in section 3.2.1, mainly targeting SoC-attached FPGAs. In this section, we are detailing the host-guest communication extensions developed focusing on the virtualization of PCIe FPGAs. In particular, in WP3 we focused at finding a way to notify the host when an FPGA kernel is in use to properly manage the FPGA accelerators lifecycle. The use case we imagined for the EVEREST project involves having multiple VMs, each with one VF (FPGA kernel) attached. Such VF can be detached anytime by the virtualization framework in the host via di ESFM program. From the VMs point of view, this event is not predictable and can lead to a critical/inconsistent state that brings to a kernel panic in the VM or eventually a crash in the host.

As a result, there is a need to enable communication between the host tool for the detachment (ESFM) and the virtual machine driver to make sure that nor the VM or the host reach an inconsistent state. In this way, the detach operation from the host can happen only when the guest is not actively using the FPGA. As shown in figure 4, the VF driver in the VM takes care of informing the Physical Function (PF) about what VM is using what VF (Step 1-2). The PF driver handles the requests of multiple VFs keeping track of the state of each accelerator (step 3). State information are then accessible to ESFM via *sysfs*, a common mechanism used by drivers to get information to host user space; for that reason, due to the changes done to the PF driver, it creates a new file in the *sysfs* that a host user space program can read to know which kernel is in use and by which VM. Consequently, when the user request an accelerator detachment (step 4), ESFM is able to read the sysfs configuration (step 5) and only if possible forwards the request to the PF driver (step 6) that can proceed with the detachment (step 7).

### 3.2.2 Data management techniques for the cloudFPGA platform

One of the foundational tasks of the workload processing on a heterogeneous system, like the EVEREST platform, is the data movement in and out of the discrete computing resources. In the case of cloudFPGA, as one of the computing nodes of the EVEREST platform, the primary medium to transfer data is the network. In the deliverable D3.1 we explained the data management techniques for the IBM cloudFPGA platform in detail. The continuous evaluation of the requirements for EVEREST as well as repeated performance tests confirmed that the architecture presented in Figure 5 and Table 3 initially reported in Deliverable D3.1 still fulfill the requirements of the project, thus it was not changed in the second part of the project. With the purpose of making this deliverable a self contained document, the remaining part of this subsection, summarizes the description of the data management techniques for the cloudFPGA platform that were extensively presented in Deliverable D3.1, reporting here from the same deliverable also all the needed architectural figures, block

Figure 4 – VMs guests-host communication for detachment overview.

diagrams, and tables relevant for the explanation.

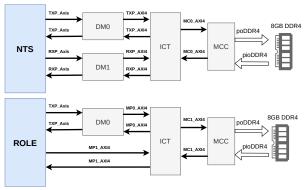

IBM has developed a TCP/UDP offload engine on the FPGA logic. The FPGA developer is provided with the option to move network data to an AXI memory map (MM) interface or to an AXI4-Stream interface, inside the FPGA. The data can be processed directly at line-rate or they can be buffered at the DRAM of the cloudFPGA module.

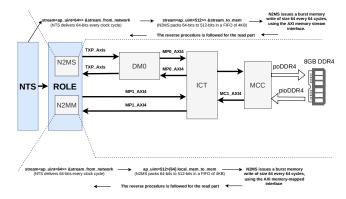

The cFDK offers two Shells, the Kale and the Themisto. Both shells provide access to the "MEM" subsystem in order to interact with two physical DDR4 memory modules. A block diagram of MEM is depicted in Fig. 5. The memory channel #0 (MC0) is dedicated to the network transport stack (NTS) of the Shell. The user's application has full access to the 8 GB of memory channel #1 (MC1).

Figure 5 – Overview of the cloudFPGA memory subsystem ("MEM").

Table 3 lists the sub-components of MEM and provides a link to their documentation as well as their architecture body.

| Entity              | Description                   | Architecture            |

|---------------------|-------------------------------|-------------------------|

| MEM                 | Memory Sub-System             | memSubSys               |

| MEM/MC0             | Memory Channel 0              | memChan_DualPort        |

| MEM/MC1             | Memory Channel 1              | memChan_DualPort_Hybrid |

| MEM/MC[0,1]/DM[0,1] | AXI Data Mover                | PG022                   |

| MEM/MC[0,1]/ICT     | AXI Interconnect              | PG059                   |

| MEM/MC[0,1]/MCC     | UltraScale Architecture-Based | PG150                   |

Table 3 – The sub-components of cloudFPGA MEM module.

EST we choose to provide both popular interfaces for Xilinx FPGAs, i.e. an AXI4-full and an AXI4 stream. This is achieved by implementing, as part of the Themisto Shell and the cFDK, an AXI DataMover and an AXI Interconnect module to interface the ROLE to the physical DDR4 module. The AXI DataMover is a key interconnect infrastructure IP that enables high throughput transfer of data between the AXI4 memory-mapped and AXI4-Stream domains.

**Network to DRAM buffering.** Instead of having the accelerator to handle the network data directly, two soft-modules, namely N2MS and N2MM, can process the network data stream and store it in the DRAM, using either an AXI streaming interface or a memory interface respectively. As shown in Fig. 6, the network stream is accumulated to a local memory until a payload of 4KB is reached. A 4KB burst write follows. From that moment, a notification signal is raised to inform the accelerator that there are data into the memory so that the processing can start. While the accelerator is processing the data, the N2MS and N2MM engines are working independently. This allows the accelerator to utilize the entire bandwidth of the DRAM module over the AXI interface. If the accelerator is programmed in C++/HLS, the #pragma dataflow directive can be employed to allow for an initiation interval (II) of 1. This allows the accelerator's pipeline to be utilized at every clock cycle.

Figure 6 – A cF data management technique to optimize accelerator throughput.

**Network payload encapsulation.** Another DMT deals with the encapsulation of special data over the TCP/UDP payload. For such cases in cF we provide two ways of handling such data:

- Through an AXI Lite memory-mapped channel provided by Themisto Shell.

- Through encapsulation over the TCP/UDP payload. The user has the freedom to encapsulate a custom data header of arbitrary length (less than the configured MTU) into the UDP/TCP payload.

#### 3.2.3 Data management techniques for Xilinx Alveo accelerators

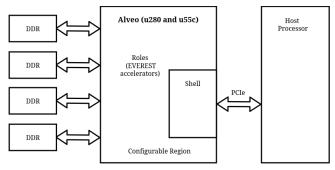

In Deliverable D3.1 we introduced the Xilinx support for the Alveo accelerators. Here we discuss how this support is leveraged in EVEREST. As presented in the Xilinx website [1], that is here summarized, the Alveo card targeted in EVEREST have three essential features: a powerful and large FPGA for deploying the accelerator, a high-bandwidth memory architecture with multiple (virtual) channels, and an high-bandwidth PCIe link to connect to a host server. Alveo designs have a conceptual model similar to cloudFPGA designs with a **shell** and a **role**. The shell contains all the static functionality, while the accelerator generated by the EVEREST SDK are deployed in the role. This topology is reflected in Figure 7 [1].

The Alveo FPGA cards used in EVEREST (u280 and u55c) feature from 8 to 16 GB of High-Bandwidth Memory (HBM2) at 460GB/s of bandwidth that can be used for exploit data-level parallelism over multiple accelerator instances (cf. Olympus optimizations in Deliverable D4.5). This memory region is referred to as the *device global memory*. It requires the host code to transfer data accordingly to how the accelerators will use them. For this reason, the hardware generation flow developed in EVEREST requires to produce not only the hardware modules but also the corresponding software functions.

In addition, AXI lines between the global memory and the accelerators are 256 bits large, allowing for transferring more data at the same time. However, such data must properly received, stored, and used by the accelerators to avoid communication bottlenecks.

Figure 7 - Conceptual topology of Alveo devices, adapted from Xilinx website [1]. EVEREST accelerators are implemented in the role part

Specific to the design of the EVEREST accelerators, it is the points that are relevant for the DMT are:

- Moving data between the host and the global device memory is expensive. Such communication overheads must be hidden by properly balancing computation and communication.

- High bandwidth between the HBM channels and the FPGA logic must be properly exploited to achieve high throughput.

- Within the FPGA fabric, logic can be efficiently deployed with HLS but requires methods to efficiently use the limited on-chip storage resources.

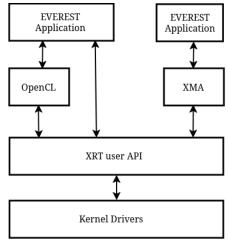

Figure 8 – XRT Software Stack adapted from Xilinx Website [1]. EVEREST user-defined drivers rely on the XRT APIs to control the underlying hardware.

The Xilinx Runtume (XRT) is a low-level API, and can be used directly or it can be interfaced using higher level APIS, such as OpenCL or XMA. Essentially, the role of XRT is to program and to manage operation and the life cycle of the Alveo card kernels and allocating and migrating the memory between host and card. Figure 9, adapted from the official Xilinx website [1] shows the standard top-level view of the available APIs. In EVEREST we are utilizing both the high-level OpenCL and the low-level XRT APIs where the accelerator drivers produced in WP4 can move the data accordingly to the generated hardware. For example, data buffer must be filled in accordingly to the data layout defined for the accelerators. In general, the EVEREST code is complementary to and leverages the XRT Software Stack to control the accelerators.

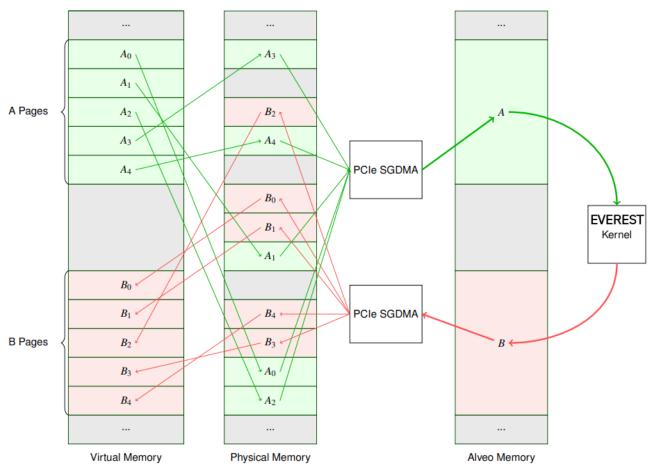

The memory of the EVEREST Alveo-based platform has six attributes. Given a pointer to a data buffer, that data pointer may be virtual or physical. The memory to which it points may be paged or physically contiguous. And, finally, from the standpoint of the processor that memory may be cacheable or non-cacheable.

An allocated memory space on the host side results in virtual page addresses of 4KiB. Moving those pages to Alveo's memory will result in resolving virtual page addresses to physical memory addresses. The next step is the assembling of these physical addresses into a scatter gather list to enqueue to a DMA engine with scatter-gather capability, which would then copy those pages one-by-one to their destination. The reverse work is followed for moving a buffer from Alveo to a virtual, paged address rang on host memory.

Figure 9 depicts a simplified view of the system, while the virtual to physical mapping is reported in Figure 10. For performance reasons, within the Alveo card, accelerators operate only on physical memory addresses and data is always stored contiguously.

Figure 9 - Virtual Memory Transfer to/from Alveo

Building and managing those scatter gather lists and managing the page tables can become time consuming even for a fast host processor. It's much easier to build a scatter gather list, though, if all of the pages are contiguous in physical memory. Modern operating systems provide memory allocators for this purpose. In EVEREST we exploit this DMT to decrease the complex logic of advanced scatter-gather DMA lists. This results in lower FPGA resource utilization and lower latency in host-FPGA memory operations.

#### 3.2.4 HLS data management techniques

In this subsection we update the description of the data management techniques done at the HLS level. We concentrated on loop pipelining and custom data types. Our description start from the text, figures, and tables previously reported in Deliveralble D3.1, which have been update where needed, most notably in the addition of new results on the HLS optimization, obtained in the second part of the project and in the description of the cluster level communication.

Considering the data processing at the level of the FPGA accelerator leads to the analysis of data access patterns, and of the alignment of data accesses with the width of the memory. This allows defining where the HLS directives characterizing the memory access pattern should be inserted together with unrolling directives and loop transformations to ensure alignment and improve performance. Another example is provided by transformations like loop pipelining when applied at a higher level (e.g., MLIR), as they can take into account latency-insensitive memory accesses and increase the instruction-level parallelism. In the following sections of the deliverable we elaborate on some of the techniques that we exploit in EVEREST.

#### 3.2.4.1 Loop pipelining

Loop pipelining aims at overlapping the execution of multiple loop iterations. This technique has been successfully used in compiler infrastructures for decades [43], and it generally consists of two steps: loop scheduling and code generation. Depending on the available computation and memory resources, and if interiteration data dependencies allow it, a pipelined loop can issue the execution of a new iteration at every clock cycle.

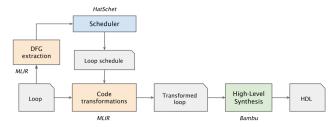

The proposed approach aims to leverage high-level code optimizations to provide a hardware-oriented input description to High-Level Synthesis. Fig. 10 shows the main steps and tools involved: the input code contains a loop to be pipelined, so the code is first passed to a scheduler to obtain a loop iteration schedule. Then, we implement code transformations that work on the input code and use the schedule to produce the pipelined loop. The resulting code is finally translated and processed by the HLS tool to generate an accelerator description in Verilog/VHDL.

Figure 10 - Overview of the optimization flow for synthesis-oriented loop pipelining starting from MLIR description.

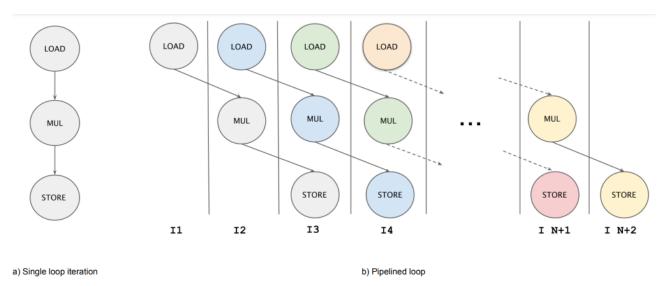

As previously mentioned, loop pipelining requires a scheduling phase and a code generation phase; we will introduce here a simple example that will be useful to illustrate these steps more in detail. Let us consider a for loop that reads values from an array, multiplies them with a constant, and writes them into another array. A single iteration of this simple loop contains three operations: load, multiply, and store. Figure 11 represents the data flow graph of one iteration; clearly, the three operations depend on each other and cannot be parallelized.

Figure 11 - Creation of a pipelined loop.

Loop pipelining allows scheduling operations from different original iterations together: as these operations would not depend on each other, they could be executed in parallel without constraints. The result is shown in Figure 11b), where each column represents one iteration of the new loop, and operations originating from the same original iteration use the same color. By overlapping original iterations, loop pipelining eliminates the parallelization constraints: all operations within the same iteration are independent now, so they can be executed in parallel. Incomplete iterations at the beginning form a loop prologue; the last few iterations are also incomplete, and they form a loop epilogue. The new loop is built of the complete iterations between prologue and epilogue. In the example shown in Figure 11b), iterations I1 and I2 belong to the loop prologue, I N+1 and D3.2 - Data management techniques: final version

I N+2 represent the epilogue, while the actual new loop starts from I3. If we assume that all functional units execute in one clock cycle, the achieved II in this simple example is equal to 1, as shown in Fig. 12.

| CYCLE | LOAD0 | STORE0 | MUL0 |                        |

|-------|-------|--------|------|------------------------|

| 0     | LOAD  |        |      | PROLOGUE               |

| 1     | LOAD  |        | MUL  | FROLOGUE               |

| 2     | LOAD  | STORE  | MUL  |                        |

| 3     | LOAD  | STORE  | MUL  | NEW LOOP<br>ITERATIONS |

|       |       |        |      |                        |

| N+1   |       | STORE  | MUL  | } EPILOGUE             |

| N+2   |       | STORE  |      | ) Li ilodol            |

Figure 12 – Pipelined loop schedule.

Within the proposed flow, scheduling is performed by HatSchet, and code generation is implemented as a set of transformations in MLIR; the pipelined loop is then passed to Bambu to obtain an HDL implementation. It represents an alternative to other loop pipelining approaches that delegate scheduling and pipelining to the HLS tool itself. Bringing loop pipelining (and possibly other optimizations) outside the scope of the HLS tool has significant advantages: for example, the developer is more in control of the applied techniques, as their effects are visible in the transformed IR. Moreover, applying transformations on a specialized, higher-level abstraction increases flexibility, portability, and requires less time than implementing and exploring different techniques within the HLS tool. Furthermore, MLIR is built to allow easy integration between different optimizations: this means that loop pipelining may be combined with other techniques to create inputs to the HLS tool that are more appropriate to generate efficient hardware accelerators. The results of the proposed approach for loop pipelining applied to Polybench kernels are presented in Table 4.

| Benchmark | Baseline (cycles) | Pipelined (cycles) | Speedup |

|-----------|-------------------|--------------------|---------|

| 2mm       | 214.914           | 76.482             | x2.81   |

| 3mm       | 304.576           | 117.428            | x2.59   |

| atax      | 41.911            | 16.869             | x2.48   |

| bicg      | 41.887            | 8.749              | x4.79   |

| doitgen   | 130.742           | 69.222             | x1.89   |

| gemm      | 244.622           | 83.002             | x2.95   |

| gemver    | 90.122            | 25.845             | x3.49   |

| mvt       | 43.362            | 16.722             | x2.59   |

| syr2k     | 227.582           | 70.910             | x3.21   |

| syrk      | 153.182           | 57.490             | x2.66   |

| trmm      | 74.362            | 37.392             | x1.99   |

Table 4 – Performance of selected Polybench kernels: baseline and MLIR loop pipelining.

The modularity and flexibility provided by MLIR allow to introduce optimizations, as we did with affine loop pipelining, and to experiment with existing ones, to generate optimized IRs for HLS. The affine dialect provides a growing set of loop-oriented transformations as compiler passes, which can easily be enabled or disabled. Even if some of them are also available as backend HLS optimizations triggered by pragmas, applying them at the MLIR level allows to decouple loop optimizations (which do not necessarily require hardware-related considerations) from the backend HLS tool, and thus enhance portability.

Loop pipelining can provide performance benefits on its own, but it can also be coupled with different optimizations to explore different design points with different performance/area trade-offs. We explored a few different options on the gemm kernel with the Bambu backend: Table 5 shows that it can be beneficial to increase the number of iterations in the pipelined loop through loop permutation, which reduces the number D3.2 - Data management techniques: final version

of cycles with a minimal increase in resource utilization. If we increase the size of the loop body through unrolling, instead, we obtain an even faster design at the cost of significant area consumption. The same exploration of design points would require manual modifications on the code when done at the C/C++ level; for typical HLS optimizations such as loop unrolling, this can be as simple as adding a pragma, but it can require significant code rewriting for other transformations (including loop permutation). In an MLIR-based design flow, optimizations can be exposed as compiler passes and compiler options that are easier to enable/disable in a design space exploration phase.

| Optimizations                 | Cycles | DSPs | LUTs  | Slices | Registers | Frequency  | Speedup  | Slices overhead |

|-------------------------------|--------|------|-------|--------|-----------|------------|----------|-----------------|

| none                          | 157122 | 10   | 1678  | 724    | 1397      | 102.27 MHz | baseline | baseline        |

| loop pipelining               | 82362  | 20   | 3024  | 1303   | 3576      | 101.48 MHz | 1.91x    | 1.80x           |

| loop permutation + pipelining | 81182  | 20   | 3006  | 1306   | 3413      | 100.94 MHz | 1.93x    | 1.80x           |

| loop unrolling + pipelining   | 17642  | 100  | 21380 | 8075   | 18671     | 90.39 MHz  | 8.91x    | 11.15x          |

Table 5 - Effect of affine optimizations on gemm (double, mini) synthesized by Bambu.

#### 3.2.4.2 Custom data types

Most of the HPC applications deployed on cloud servers deal with complex computation flows operating on floating-point data. Floating-point data types are commonly provided in two formats only, single- and double-precision, and therefore, if the computation does not fully exploit the available range, floating-point calculations result in wasted precision and power consumption. It is not worth addressing this waste when targeting CPU execution, since arithmetic units in modern general-purpose processors are highly optimized to handle single-and double-precision data types, and even if software-based implementations of smaller precision floating-point types are available (e.g., through the MPFR library), they usually bring no improvement to the computation time nor the power consumption.

When designing a hardware accelerator, on the other hand, it is possible to generate ad-hoc functional units able to deal with custom data types. In this case, an application able to exploit computation on floating-point data with smaller bitwidth is able to benefit from this technique in many aspects: when targeting FPGAs, it may result in significant improvement in computation latency and resource usage, which can lead to faster and more power-efficient accelerator designs. Furthermore, with a smaller bitwidth memories can be restructured resulting in a smaller memory footprint and faster memory accesses during the computation flow.

Automated generation of custom floating-point functional units is available within the EVEREST SDK [31], and high-level optimization phases are able to exploit it if the considered application, or part of it, can benefit from this technique. At the end of the optimization flow, custom precision floating-point types are implemented and integrated into the accelerator design by the PandA-Bambu HLS tool (details are in Deliverable D4.2).

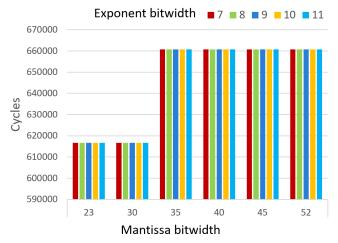

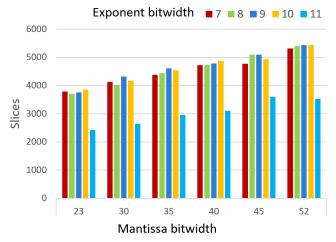

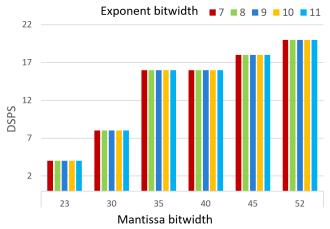

In software, floating-point formats are mainly based on the IEEE standard, and their precision is classified from half to quadruple. Most of the processors available provide a hardware implementation of single- and double-precision functional units. Only recently they have started to add hardware support to half-precision (see FP16 or BFLOAT16 formats), mainly because of their use in artificial intelligence applications. In an FPGA accelerator, however, designers have more freedom to choose different formats, for example by relaxing the number of bits required for the mantissa and exponent. This is a parameter that can be considered during the EVEREST code-variant generation to generate alternatives that allow the run-time system to trade off accuracy against resource consumption on the FPGA fabric. This has been achieved by integrating support for parametric floating-point formats (with a variable number of bits of exponent and mantissa) into the higher-level compiler infrastructure and into the HLS engine that generates the hardware accelerators.

To allow optimization of floating-point data during the HLS process, we relaxed the constraints on the number of bits of the mantissa and exponent of the IEEE 754 standard. We do not consider our approach, called TrueFloat, to be a novel data type, since it is based on existing standards and uses their representation and format. The novelty of TrueFloat lies in the fact that it allows the HLS tool to optimize floating-point operations before producing the Verilog: this is not possible in current approaches based on predefined RTL cores, where the implementation of the floating-point operations is taken from a library without optimization at the HLS level. Comparisons on basic floating-point operators such as adder, multiplier, and divider have been

Table 6 – Custom precision floating-point adder.

|            |       | TrueFloat |      |        |           | FloPoCo |      |        |           | Template HLS |      |        |           |

|------------|-------|-----------|------|--------|-----------|---------|------|--------|-----------|--------------|------|--------|-----------|

| Target     | Spec  | Slices    | LUTs | Cycles | Frequency | Slices  | LUTs | Cycles | Frequency | Slices       | LUTs | Cycles | Frequency |

|            | e9m38 | 193       | 584  | 6      | 104.21    | 163     | 534  | 5      | 104.76    | 192          | 519  | 9      | 101.90    |

| Zynq7000   | e8m23 | 122       | 340  | 5      | 101.06    | 103     | 291  | 5      | 104.49    | 125          | 300  | 8      | 109.16    |

| 100MHz     | e5m10 | 57        | 157  | 4      | 103.38    | 52      | 160  | 5      | 109.86    | 71           | 159  | 8      | 158.81    |

| TOOMINZ    | e3m4  | 28        | 93   | 4      | 113.01    | 23      | 70   | 4      | 117.20    | 43           | 93   | 7      | 164.96    |

|            | e9m38 | 185       | 590  | 6      | 205.42    | 193     | 545  | 8      | 208.89    | 219          | 508  | 10     | 268.96    |

| Virtex7    | e8m23 | 123       | 363  | 5      | 216.54    | 118     | 337  | 7      | 223.76    | 133          | 338  | 9      | 223.31    |

| 200MHz     | e5m10 | 54        | 161  | 4      | 215.10    | 48      | 161  | 6      | 239.12    | 63           | 143  | 8      | 259.13    |

| 2001011 12 | e3m4  | 26        | 81   | 4      | 235.34    | 29      | 76   | 6      | 306.74    | 38           | 93   | 8      | 321.75    |

|            | e9m38 | 233       | 640  | 11     | 417.71    | 207     | 566  | 14     | 360.23    | 253          | 638  | 17     | 413.22    |

| Virtex7    | e8m23 | 141       | 390  | 8      | 394.16    | 126     | 254  | 12     | 370.23    | 168          | 399  | 17     | 445.43    |

| 400MHz     | e5m10 | 75        | 164  | 6      | 419.11    | 61      | 167  | 10     | 450.24    | 98           | 197  | 14     | 489.72    |

|            | e3m4  | 38        | 97   | 6      | 408.83    | 41      | 94   | 9      | 414.07    | 55           | 124  | 13     | 524.93    |

carried out against two other research tools: FloPoCo [26] and Template HLS [51]. Both these implementations exploit a custom floating-point representation slightly different from the IEEE 754 standard to achieve a simpler exception handling without impacting precision, at the cost of two additional bits: thus, a double-precision floating-point which requires 64 bits to be represented in the IEEE 754 format would require 66 bits to be represented in the FloPoCo format used in [26] and [51]. An indirect comparison with commercial floating-point cores (e.g., from Xilinx, Altera) is possible since FloPoCo has been already compared with such cores as presented in [29]. Table 6, Table 7, and Table 8 show results of the synthesis for the three floating-point operators for each one of the described implementations. Two different Xilinx FPGA boards have been used, a Zynq7000 (xc7z020clg484-1) and Virtex7 (xc7vx485tffg1761-2), and three different target frequencies (100MHz, 200MHz, 400MHz) have been selected to achieve a fair comparison also considering the flexibility of each solution. TrueFloat operators are synthesized into Verilog code using Bambu HLS, while Verilog operators from the Template HLS library are generated using Xilinx Vitis HLS 2021.2. All accelerators are synthesized using Xilinx Vivado 2021.2 and results are reported after implementation. Five floating-point formats are explored by the benchmark:

- e9m38 9-bits exponent, 38-bits mantissa

- e8m23 8-bits exponent, 23-bits mantissa (IEEE 754 single precision)

- e5m10 5-bits exponent, 10-bits mantissa (IEEE 754 half precision)

- e3m4 3-bits exponent, 4-bits mantissa

The proposed approach is quite consistent in delivering a design close to the target frequency while still being competitive with respect to FloPoCo [26] and Template HLS [51] both in terms of latency and resource usage. Results for the TrueFloat floating-point addition (Table 6) are quite similar to FloPoCo ones while our approach is able to achieve a better latency with higher target frequencies. The same stands for floating-point multiplication (Table 7): the TrueFloat multiplication core employs a Karatsuba multiplier as its core multiplying unit, which proves to be quite resilient to different frequencies requirements, while FloPoCo and Template HLS exploit a bit heap to perform the same task. The use of a bit heap seems to be better in terms of resource footprint, but is not suitable for clock-frequencies optimization and thus resulting in slower designs. Finally, similar considerations may be extended to the floating-point division unit (Table 8): the TrueFloat implementation relies on a loop to perform the long division, thus resulting in a non-pipelined core. Conversely, FloPoCo and Template HLS exploit an unrolled version of the base-4 long division algorithm, which is suitable for pipelining, but yields much higher impact on resource usage.

The aforementioned benchmark setup does not include EVEREST platforms like Kintex and Alveo boards, which are evaluated separately in Table 9.

Floating-point cores for the Posit representation have not been considered so far, since Posit can not be considered as a simple drop-in replacement for standard IEEE754 floating-point data types, as discussed in [25]. There are many differences in number accuracy throughout the range of represented values between IEEE754 and Posit encoding, operators' behavior may differ and an accurate analysis of the application may be required before applying such a radical transformation. Furthermore, as shown in [30], performance and

#### Table 7 – Custom precision floating-point multiplier.

|                    | TrueFloat |        |      |      | FloPoCo |           |        |      |      | Template HLS |           |        |      |      |        |           |

|--------------------|-----------|--------|------|------|---------|-----------|--------|------|------|--------------|-----------|--------|------|------|--------|-----------|

| Target             | Spec      | Slices | LUTs | DSPs | Cycles  | Frequency | Slices | LUTs | DSPs | Cycles       | Frequency | Slices | LUTs | DSPs | Cycles | Frequency |

|                    | e9m38     | 133    | 331  | 8    | 6       | 111.55    | 80     | 216  | 6    | 3            | 74.96     | 77     | 153  | 5    | 4      | 105.29    |

| 7.ma7000           | e8m23     | 46     | 92   | 2    | 4       | 118.35    | 44     | 68   | 2    | 3            | 84.37     | 41     | 47   | 2    | 3      | 122.25    |

| Zynq7000<br>100MHz | e5m10     | 27     | 50   | 1    | 4       | 126.05    | 15     | 27   | 1    | 3            | 108.71    | 24     | 38   | 1    | 6      | 185.22    |

| TOOMINZ            | e3m4      | 23     | 57   | 0    | 4       | 105.51    | 14     | 38   | 0    | 3            | 122.83    | 16     | 41   | 0    | 3      | 145.12    |

|                    | e9m38     | 144    | 333  | 8    | 7       | 232.99    | 99     | 256  | 6    | 4            | 163.15    | 88     | 156  | 5    | 5      | 223.11    |

| Virtex7            | e8m23     | 48     | 91   | 2    | 5       | 220.60    | 47     | 69   | 2    | 4            | 177.39    | 38     | 44   | 2    | 4      | 221.68    |

| 200MHz             | e5m10     | 29     | 47   | 1    | 4       | 230.14    | 23     | 28   | 1    | 3            | 197.39    | 27     | 38   | 1    | 6      | 397.30    |

| 200101112          | e3m4      | 21     | 59   | 0    | 4       | 245.63    | 13     | 37   | 0    | 3            | 255.29    | 17     | 41   | 0    | 3      | 278.94    |

|                    | e9m38     | 224    | 400  | 8    | 15      | 411.18    | 144    | 284  | 6    | 6            | 255.29    | 84     | 106  | 5    | 10     | 250.13    |

| Virtex7            | e8m23     | 75     | 126  | 2    | 11      | 498.50    | 44     | 79   | 2    | 5            | 301.11    | 55     | 58   | 2    | 10     | 523.56    |

| virtex/<br>400MHz  | e5m10     | 31     | 62   | 1    | 5       | 396.98    | 31     | 40   | 1    | 4            | 252.20    | 34     | 39   | 1    | 9      | 556.48    |

| 4001017            | e3m4      | 26     | 66   | 0    | 4       | 407.66    | 23     | 42   | 0    | 4            | 369.95    | 28     | 46   | 0    | 6      | 456.41    |

Table 8 – Custom precision floating-point divider.

|                    | TrueFloat |        |      |        | FloPoCo   |        |      |        | Template HLS |        |      |        |           |

|--------------------|-----------|--------|------|--------|-----------|--------|------|--------|--------------|--------|------|--------|-----------|

| Target             | Spec      | Slices | LUTs | Cycles | Frequency | Slices | LUTs | Cycles | Frequency    | Slices | LUTs | Cycles | Frequency |

|                    | e9m38     | 191    | 566  | 26     | 127.48    | 478    | 1603 | 14     | 73.96        | 847    | 2188 | 28     | 127.19    |

| 7una7000           | e8m23     | 123    | 360  | 18     | 149.85    | 235    | 660  | 9      | 79.30        | 304    | 780  | 16     | 131.22    |

| Zynq7000<br>100MHz | e5m10     | 62     | 172  | 12     | 159.79    | 77     | 205  | 6      | 102.10       | 91     | 258  | 8      | 116.90    |

| TOOMINZ            | e3m4      | 34     | 104  | 8      | 171.73    | 36     | 91   | 4      | 109.90       | 43     | 109  | 7      | 174.00    |

|                    | e9m38     | 195    | 564  | 26     | 253.16    | 504    | 1453 | 16     | 168.86       | 678    | 2012 | 24     | 222.22    |

| Virtex7            | e8m23     | 119    | 359  | 18     | 277.39    | 221    | 626  | 11     | 154.96       | 357    | 860  | 19     | 254.26    |

| 200MHz             | e5m10     | 68     | 180  | 12     | 238.37    | 91     | 234  | 7      | 215.56       | 105    | 274  | 10     | 251.07    |

| 200101112          | e3m4      | 32     | 99   | 8      | 302.38    | 39     | 103  | 5      | 231.64       | 37     | 106  | 7      | 313.87    |

|                    | e9m38     | 311    | 669  | 49     | 340.71    | 640    | 1562 | 31     | 213.49       | 1250   | 2876 | 58     | 404.04    |

| Virtex7            | e8m23     | 190    | 411  | 19     | 344.35    | 253    | 645  | 20     | 236.12       | 544    | 1197 | 37     | 417.19    |

|                    | e5m10     | 75     | 187  | 12     | 404.69    | 80     | 195  | 11     | 252.33       | 174    | 367  | 22     | 473.93    |

| 400MHz             | e3m4      | 48     | 131  | 9      | 438.21    | 58     | 110  | 8      | 418.23       | 72     | 144  | 13     | 462.11    |

Table 9 – TrueFloat custom precision operators on the EVEREST target boards.

|                         | Adder |        |      |        | Multiplier |        |      |      |        | Divider   |        |      |        |           |

|-------------------------|-------|--------|------|--------|------------|--------|------|------|--------|-----------|--------|------|--------|-----------|

| Target                  | Spec  | Slices | LUTs | Cycles | Frequency  | Slices | LUTs | DSPs | Cycles | Frequency | Slices | LUTs | Cycles | Frequency |

| Kintex                  | e9m38 | 113    | 585  | 5      | 266.31     | 85     | 365  | 8    | 6      | 262.88    | 134    | 679  | 27     | 282.97    |

| UltraScale              | e8m23 | 160    | 827  | 5      | 247.52     | 90     | 32   | 5    | 2      | 298.42    | 88     | 441  | 18     | 301.57    |

| 250MHz                  | e5m10 | 44     | 216  | 4      | 286.86     | 17     | 62   | 1    | 4      | 288.10    | 46     | 204  | 12     | 292.48    |

| ZOUVITZ                 | e3m4  | 24     | 99   | 4      | 295.51     | 20     | 106  | 0    | 3      | 326.58    | 25     | 118  | 9      | 335.57    |

| Alveo                   | e9m38 | 93     | 603  | 5      | 262.19     | 78     | 323  | 8    | 5      | 270.86    | 126    | 696  | 26     | 327.65    |

| U55C                    | e8m23 | 58     | 331  | 4      | 271.37     | 22     | 89   | 4    | 2      | 292.65    | 87     | 440  | 18     | 340.25    |

| 250MHz                  | e5m10 | 39     | 195  | 4      | 278.09     | 14     | 50   | 1    | 4      | 328.62    | 49     | 204  | 12     | 378.07    |

| 230WII 12               | e3m4  | 15     | 89   | 4      | 315.76     | 25     | 106  | 0    | 3      | 441.70    | 23     | 117  | 9      | 475.06    |

| Alvoo                   | e9m38 | 102    | 583  | 5      | 250.44     | 76     | 322  | 8    | 5      | 278.32    | 123    | 696  | 26     | 313.68    |

| Alveo<br>U280<br>250MHz | e8m23 | 61     | 334  | 4      | 273.22     | 25     | 89   | 2    | 4      | 278.32    | 86     | 440  | 18     | 342.82    |

|                         | e5m10 | 41     | 194  | 4      | 275.86     | 14     | 50   | 1    | 4      | 328.62    | 47     | 204  | 12     | 357.78    |

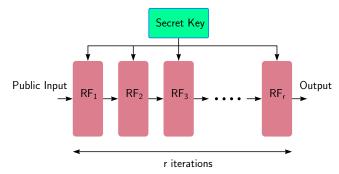

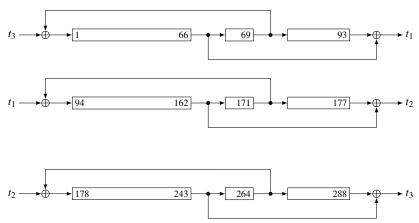

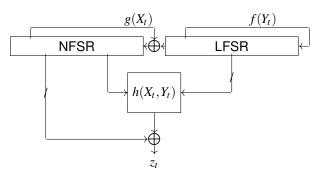

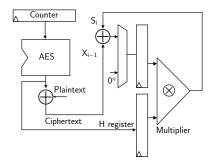

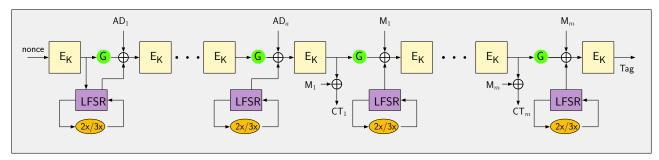

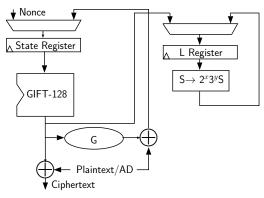

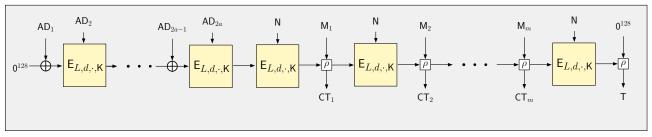

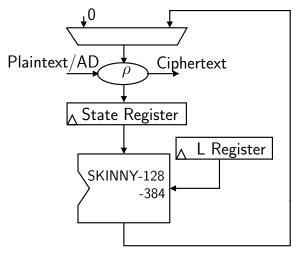

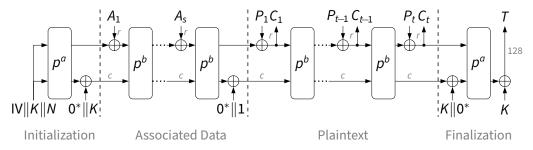

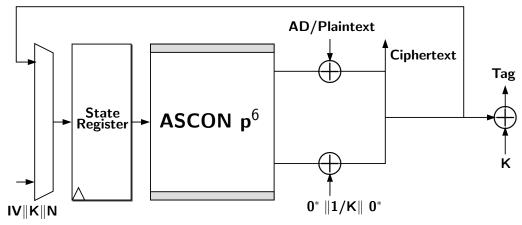

|                         | e3m4  | 19     | 91   | 4      | 312.40     | 25     | 106  | 0    | 3      | 441.70    | 23     | 117  | 9      | 475.06    |