# dEsign enVironmEnt foR Extreme-Scale big data analyTics on heterogeneous platforms

D4.5 — Final report of the compilation framework

#### **Project Summary Information**

| Project Title           | dEsign enVironmEnt foR Extreme-Scale big data analyTics on heterogeneous platforms |

|-------------------------|------------------------------------------------------------------------------------|

| Project Acronym         | EVEREST                                                                            |

| Project No.             | 957269                                                                             |

| Start Date              | 01/10/2020                                                                         |

| <b>Project Duration</b> | 42 months                                                                          |

| <b>Project Website</b>  | http://www.everest-h2020.eu                                                        |

### Copyright

© Copyright by the EVEREST consortium, 2020.

This document contains material that is copyright of EVEREST consortium members and the Expean Commission, and may not be reproduced or copied without permission.

| Num.       | Partner Name                                                          | Short Name | Country |

|------------|-----------------------------------------------------------------------|------------|---------|

| 1 (Coord.) | IBM RESEARCH GMBH                                                     | IBM        | CH      |

| 2          | POLITECNICO DI MILANO                                                 | PDM        | IT      |

| 3          | UNIVERSITÀ DELLA SVIZZERA ITALIANA                                    | USI        | CH      |

| 4          | TECHNISCHE UNIVERSITAET DRESDEN                                       | TOD        | DE      |

| 5          | Centro Internazionale in Monitoraggio Ambientale -<br>Fondazione CIMA | CIMA       | IT      |

| 6          | IT4Innovations, VSB Technical University of Ostrava                   | IT4I       | CZ      |

| 7          | VIRTUAL OPEN SYSTEMS SAS                                              | vos        | FR      |

| 8          | DUFERCO ENERGIA SPA                                                   | DUF        | IT      |

| 9          | NUMTECH                                                               | NUM        | FR      |

| 10         | SYGIC AS                                                              | SYG        | SK      |

Project Coordinator: Christoph Hagleitner Research - Zurich Research Laboratory

Scientific Coordinator: Christian Pilate - Politecnico di Milano

The technology disclosed herein may be protected by one or more patents, copyrights, trademarks and/or trade secrets owned by or licensed to EVEREST partners. The partners reserve all rights with respect to such technology and related materials. Any use of the protected technology and related material beyond the terms of the License without the prior written consent of EVEREST is prohibited.

### **Disclaimer**

The content of the publication herein is the sole responsibility of the publishers and it does not necessarily represent the views expressed by the European Commission or its services. Except as otherwise expressly provided, the information in this document is provided by EVEREST members "as is" without warranty of any kind, expressed, implied or statutory, including but not limited to any implied warranties of merchantability, fitness for a particular purpose and no infringement of third partys rights. EVEREST shall not be liable for any direct, indirect, incidental, special or consequential damages of any kind or nature whatsoever (including, without limitation, any damages arising from loss of use or lost business, revenue, profits, data or goodwill) arising in connection with any infringement claims by third parties or the specification, whether in an action in contract, tort, strict liability, negligence, or any other theory, even if advised of the possibility of such damages.

#### **Deliverable Information**

| Work-package               | WP4                                       |

|----------------------------|-------------------------------------------|

| Deliverable No.            | D4.5                                      |

| Deliverable Title          | Final report of the compilation framework |

| Lead Beneficiary           | TUD                                       |

| Type of Deliverable        | Report                                    |

| <b>Dissemination Level</b> | Public                                    |

| Due Date                   | 31/01/2024                                |

#### **Document Information**

| <b>Delivery Date</b> | 18/03/2024                                                                                                                                                                                                                                         |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| No. pages            | 54                                                                                                                                                                                                                                                 |

| Version   Status     | 0.6   Final                                                                                                                                                                                                                                        |

| Responsible Person   | Jeronimo Castrillon (TUD)                                                                                                                                                                                                                          |

| Authors              | Jeronimo Castrillon (TUD), Karl A. F. Friebel (TUD), Felix Suchert (TUD)) Burkhard Ringlein (IBM), Serena Curzel (PDM), Michele Fiorito (PDM), Pubrizio Ferrandi (PDM), Donatella Sciuto (PDM), Christian Pilato (PDM), Steplania, Soldavini (PDM) |

| Internal Reviewer    | Francesco Regazzoni (USI)                                                                                                                                                                                                                          |

The list of authors reflects the major contributors to the activity describes in the document. All EVEREST partners have agreed to the full publication of this document. The list of authors does not imply any claim of ownership on the Intellectual Properties described in this document.

### **Revision History**

| Date       | Ver. | Author(s)                 | mmary of main changes                                                            |

|------------|------|---------------------------|----------------------------------------------------------------------------------|

| 24.11.2023 | 0.1  | Jeronimo Castrillon (TUD) | Initial structure.                                                               |

| 04.01.2024 | 0.2  | Jeronimo Castrillon (TUD) | Initial text, revisited structure and refined outline of the chapters.           |

| 09.02.2024 | 0.3  | Jeronimo Castrillon (TUD) | Cleaned up remaining issues in Sections 1–6. First draft of conclusions.         |

| 08.03.2024 | 0.4  | Jeronimo Castillon (TUD)  | Added tool links, requirement assessment and comparison to the state of the art. |

| 14.03.2024 | 0.5  | Christian Filato (PDM)    | Revision of hardware generation flow and general clean up.                       |

| 15.03.2024 | 0.6  | nimo Castrillon (TUD)     | Final clean up and approval.                                                     |

### **Quality Control**

| Approved by Internal Reviewer      | March 18, 2024 |

|------------------------------------|----------------|

| Approved by WP Leader              | March 15, 2024 |

| Approved by Scientific Coordinator | March 15, 2024 |

| Approved by Project Coordinator    | March 18, 2024 |

### **Table of Contents**

| 1 | EXECUTIVE SUMMARY  1.1 Structure of this Document                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6<br>6                                                         |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| 2 | OVERVIEW OF THE COMPILATION FRAMEWORK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 7                                                              |

| 3 | LANGUAGE SUPPORT  3.1 EVEREST Kernel Language                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 12<br>13                                                       |

| 4 | INTERMEDIATE REPRESENTATIONS AND TRANSFORMATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 15                                                             |

|   | <ul> <li>4.1 ekl</li> <li>4.2 esn</li> <li>4.3 dfg</li> <li>4.4 evp</li> <li>4.5 olympus</li> <li>4.6 Connecting to High-Level Synthesis (HLS)</li> <li>4.7 Machine Learning Abstractions and Optimization</li> <li>4.7.1 Operation Set Architectures</li> <li>4.7.2 DOSA: Distributed Operation Set Architectures using organic compiler principles</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                  | 16<br>17<br>19<br>20<br>22<br>22<br>23<br>24                   |

| 5 | HARDWARE GENERATION FLOW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 26                                                             |

|   | <ul> <li>5.1 Hardware-Oriented Optimizations and Kernel Generation</li> <li>5.1.1 Loop Pipelining</li> <li>5.1.2 Custom Precision Floating-point Data Types</li> <li>5.2 Partitioning to Distributed FPGAs</li> <li>5.3 Memory-Related Optimizations</li> <li>5.4 System Integration</li> <li>5.4.1 Network-attached Field Programmable Gate Arrays (FPGAs)</li> <li>5.4.2 Bus-attached FPGAs</li> </ul>                                                                                                                                                                                                                                                                                                                                         | 27<br>28<br>29<br>30<br>31<br>31                               |

| 6 | CODE GENERATION AND RUNTIME INTEGRATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 35                                                             |

|   | <ul> <li>6.1 Host Code Generation</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 35<br>35<br>36                                                 |

| 7 | FINAL ASSESSMENT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 39                                                             |

|   | 7.1 Requirements/Language and Compilers 7.1.1 REQ3.1 – W. Dexpression abstraction 7.1.2 REQ3.2 – WRF Fortran integration 7.1.3 REQ3.3 ML integration 7.1.4 REQ3.4 – Streaming support 7.1.5 REQ3.5 – Integration with compiler frameworks 7.1.6 REQ3.6 – Compiler transformations for kernels 7.1.7 REQ3.7 – Compiler transformations for dataflows 7.1.8 REQ3.8 – Multi-target code generation 7.1.9 REQ3.9 – Generation of tunable parameters 7.1.10REQ3.10 – Interface to HLS 7.1.11REQ3.11 – cFDK/OC-Accel software integration and language compatibility 7.1.12REQ3.12 – Reasoning about heterogeneous applications 7.1.13REQ3.13 – Glue code generation for heterogeneous applications 7.1.14REQ3.14 – Abstractions for offloaded kernels | 39<br>39<br>39<br>40<br>40<br>40<br>41<br>41<br>41<br>41<br>42 |

| 7.2   | Requirements: HLS and Memory Design                            | 42                   |

|-------|----------------------------------------------------------------|----------------------|

|       | 7.2.1 REQ4.1 – C/C++ support                                   |                      |

|       | 7.2.2 REQ4.2 – Bambu LLVM IR support                           |                      |

|       | 7.2.3 REQ4.3 – Bambu MLIR dialect support                      |                      |

|       | 7.2.4 REQ4.4 – HLS Verilog output                              |                      |

|       | 7.2.6 REQ4.6 – Top function specification                      |                      |

|       | 7.2.7 REQ4.7 – Block level/Top component interfaces            |                      |

|       | 7.2.8 REQ4.8 – Port-Level interfaces                           |                      |

|       | 7.2.9 REQ4.9 – Bambu Vivado HLS I/O interface interoperability |                      |

|       | 7.2.10REQ4.10 – Technology options specification               | 44                   |

|       | 7.2.11REQ4.11 – Bambu Data flow annotations                    |                      |

|       | 7.2.12REQ4.12 – Bambu OpenMP support                           | _                    |

|       | 7.2.13REQ4.13 – Bambu floating point precision                 | 45<br>45             |

|       | 7.2.14REQ4.14 – cFDK/OC-Accel top component interface          | 45<br><del>4</del> 3 |

|       | 7.2.16REQ4.16 – Software-level support                         | 45                   |

|       | 7.2.17REQ4.17 – Hardware/software data sharing                 | 45                   |

| 7.3   | Advancing the State-of-the-art                                 | 46                   |

| 0 60  | NEUTRIONE                                                      | 40                   |

| 8 60  | NCLUSIONS                                                      | 48                   |

| REFER | RENCES                                                         | 51                   |

|       |                                                                |                      |

|       |                                                                |                      |

|       |                                                                |                      |

|       |                                                                |                      |

|       |                                                                |                      |

|       |                                                                |                      |

|       |                                                                |                      |

|       |                                                                |                      |

|       |                                                                |                      |

|       |                                                                |                      |

|       |                                                                |                      |

|       |                                                                |                      |

|       |                                                                |                      |

|       | Total Set all Di                                               |                      |

|       |                                                                |                      |

|       |                                                                |                      |

|       |                                                                |                      |

|       |                                                                |                      |

|       | <b>y</b>                                                       |                      |

|       |                                                                |                      |

1

### 1 Executive Summary

The EVEREST project proposes a platform and System Development Kit (SDK) to deploy demanding work-flows to suitable high-performance or edge hardware [25, 24]. This document provides a final report on the compilation framework of the SDK. The compilation framework plays a key role in providing high-level programming support for productivity together with a methodology for optimization. The latter includes software and hardware transformations as well as autotuning support for runtime adaptivity.

In this document, we describe the technologies, tools, and components of the compilation framework and assess how they contribute to fulfilling the EVEREST requirements described in Deliverable D2.2 and Deliverable D2.5. Details on how to use the tools are provided in Deliverable D4.6. The design presented here follows the specification provided in Deliverable D4.1, which depicted a complex landscape of programming languages (Fortran, Rust, C++, Python) and computational requirements (large workflows combining High-Performance Computing (HPC), Big Data and machine learning). In this document we describe the language abstractions, high-level representations and hardware-oriented transformations for computational motifs that are representative of those found in the use cases of the EVEREST project. We use examples to demonstrate the different representations and transformations enabled in the EVEREST SDK. Use-case specific descriptions are a matter of Deliverable D6.3.

#### 1.1 Structure of this Document

This document starts with an overview of the compilation framework in Section 2. The overview details the evolution of the SDK, connecting to previous project deliverables, and describes *basecamp*, a unified tool that provides access to the multiple tools within the SDK. Section 3 summarizes contributions to Domain-Specific Languages (DSLs) and the integration into Fortran for HPC use cases. A major contribution of the SDK is a collection of Intermediate Representations (IRs) that enable reuse across comains. These IRs, implemented in Multi-Level Intermediate Representation (MLIR), are described in Section 4 along with sample transformations. Hardware programming and integration flows are described in Section 5. This includes extensions to HLS flows and system-level integration support for the EVER ST platform. The presented flow is concluded with Section 6, which describes how the components in this socument integrate with the dynamic runtime environment. In Section 7, we provide a final assessment concerning the requirements in Deliverable D2.5 and a high-level comparison with the state of the art. This onliverable finishes with conclusions in Section 8.

### 2 Overview of the Compilation Framework

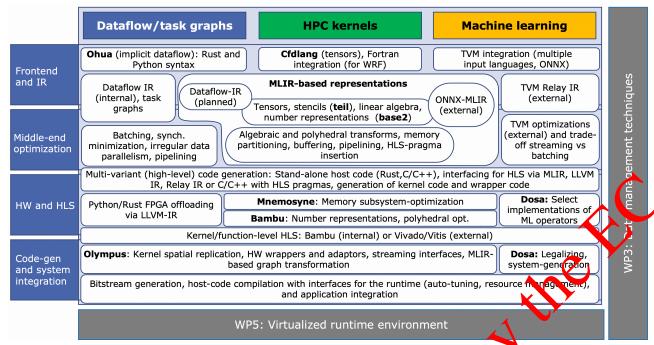

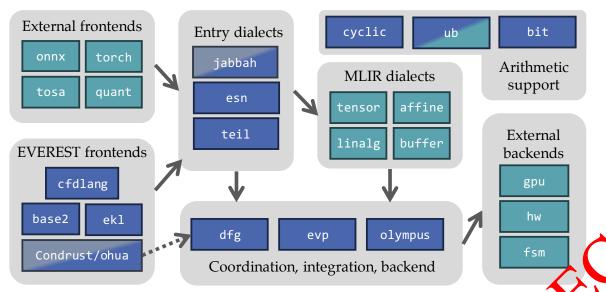

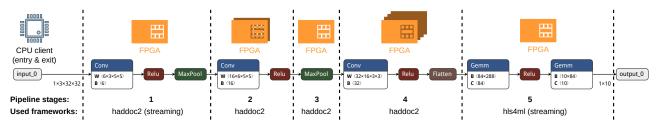

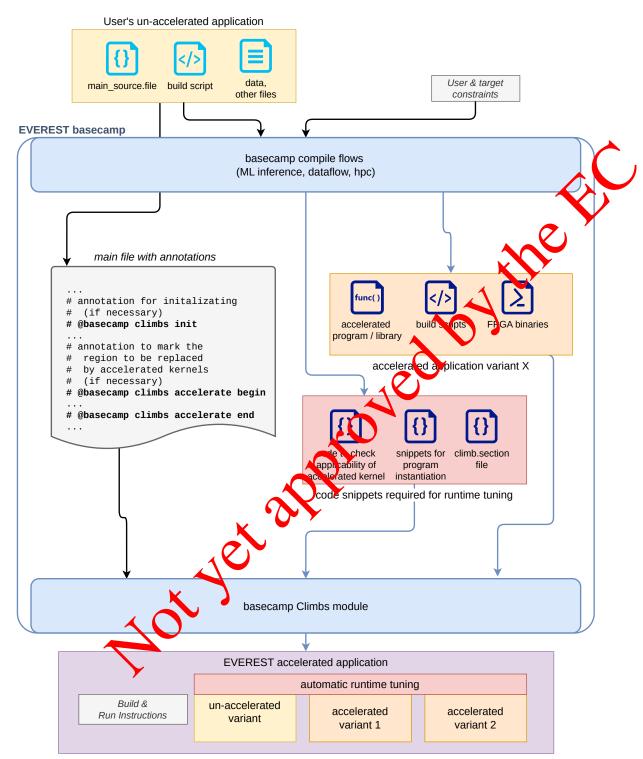

Figure 1 – Overview of the compilation flow.

Previous reports detail the evolution of the compiler tooling developed within the EVEREST project. Most notably, the evolution can be identified in Figure 1 of Deliverable D4.1, the examples of the Alpha Release in Deliverable D4.3 and in Figure 1 of Deliverable D4.2, which is replicated in Figure 1 for better reference. This figure reflects the heterogeneity of the requirements identified early in the project, with (i) different types of workloads (dataflow/task graphs, HPC kernels and machine leaning), (ii) different languages (Fortran, C/C++, ONNX, Rust, Python and DSLs), (iii) rich interfaces (via interprediate code in LLVM or MLIR, via generated C/C++ or Rust code and other metadata for variant generation), and (iv) the integration with multiple external tools and frameworks (WRF build system, TVM, the MLR intrastructure, Vivado/Vitis HLS tools.

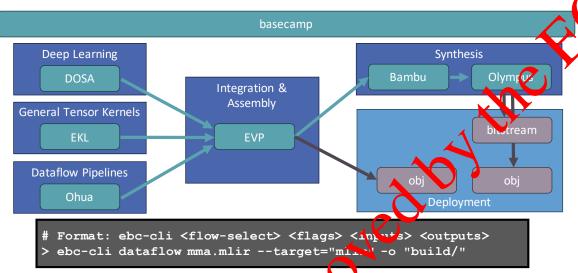

Today, the complexity depicted in Figure 1 is shalled from developers by a simple tool interface that we call *basecamp*. As shown in Figure 2, basecamp provides a common interface to pass applications to the compilation flow (see format and example at the bottom). Basecamp also interfaces with the deployment flow in EVEREST with leverages the LEXIS platorn. I, which has been extended to offload the execution of selected kernels on FPGAs. It also contains interfaces to the runtime system (see Deliverable D5.5). In this way, if an accelerated task requires more resources, the EVEREST runtime can adapt the computation accordingly.

Basecamp offers a command line interface (CLI) and a python Application Programming Interface (API), whereas the former is a grapper for the latter. The general CLI structure is shown at the bottom of Figure 2. In the given example, the outsilow tools are invoked and the result is written to the build/ directory. In that example, basecamp acts as a unified wrapper for the different optimization flows of the SDK. However, basecamp can also bundle different optimized variants of one application, i.e., different outputs of basecamp flows, together into one executable application, as described in Section 6. The complete CLI of basecamp is given in Listing 1.

<sup>1</sup> https://lexis-project.eu/web/lexis-platform/

```

ebc-cli ml_inference onnx|torchscript (--json-constraints <path-to-json-constraints> \mid --app-\leftrightarrow

\verb|name| < app-name> --target-throughput| < target-sps> --batch-size| < batch-size> -- \leftrightarrow

used\_bit\_width < used\_bit\_width > --onnx-input-name < onnx-input-name > --onnx-input-shape < \hookleftarrow

\verb|onnx-input-shape>| [--map-weights < path-to-weights-file>] < path-to-model.file> < path-to-\leftrightarrow |

output-directory> [--calibration-data <path-to-calibration-data>]

ebc-cli climbs (describe --flow <flow> | create --name <name> <path-to-file.climb> | \leftrightarrow

\verb|add_module --module < path-to-module.section> < path-to-file.climb> | add_file --file < path- \longleftrightarrow | add_file --f

to-source.file> --language <language> <path-to-file.climb> | emit <path-to-file.climb> [--\leftarrow]

output-directory <path-to-output-directory>])

ebc-cli airflow ( create | get_params | get_state | execute [--params-json-path <path-to-json-\leftrightarrow

params>]) <workflow-name>

ebc-cli -h|--help

ebc-cli -v|--version

Commands:

dataflow

Invoke the dataflow flow of the EVEREST SDK.

Invoke the HPC flow of the EVEREST SDK.

hpc

ml_inference

Invoke the ML inference flow of the EVERE

SDK.

climbs

Combine different flows (i.e.,

climbs") to one application.

airflow

Allows the execution of Airflow

via Py4Lexis.

Options:

-h --help

Show this screen.

-v --version

Show version.

-o <path-to-output>

Path to save gend

s under (defaults↔

to `generated`).

code

Target for the

nerator (supported ←

--target <target>

values: rust. mlir).

--threads <num>

\mathsf{ds} to parallelize for (\leftarrow

default: number of local cores).

--enable-parallelism <bool>

Whether t

Table the parallelization \hookleftarrow

optimization (defaults to `true`).

--c-limit <num>

of maximum collisions for computation↔

with amorphous data parallelism.

lueher to enable the transformation of \hookleftarrow

--amorphous <bool>

false`).

amorphous data parallel tasks (defaults to

-- json-constraints <path-to-json-constraints

mport the ML target constraints of the \leftrightarrow

given JSON file.

The name of the target application (to \hookleftarrow

--app-name <app-name>

create human-readable labels).

The targeted throughput (in samples-per-←

--target-throughput <target-sps>

second (sps) of the inference pp

ication.

--batch-size <batch-size>

The used batch size per inference request (i\hookleftarrow

.e. sample).

The bit width for input, activations, and \leftarrow

--used_bit_width <used-bi₩width>

weights.

The name of the input node in the ONNX graph\leftrightarrow

--onnx-input-shape ---

The input shape in the ONNX graph.

--map-weights <path-to-weights-file>

The file containing the weights for the \hookleftarrow

kernel-weight-mapping schema.

--calibration-data <path-to-calibration-data>

Point to the .npy file containing example \leftrightarrow

data to calibrate transformation to quantized data types.

describe

Describe the required API for the flow.

Specifies the flow to describe.

--flow <flow>

create

Create a new flow.

add_module --module

Add a new application variant to an existing↔

1

climb.

add_file --file

Add a file (with annotations) of the main \hookleftarrow

application to the climb.

--language <language>

The language of the added file. Currently \hookleftarrow

supported are: python, docker, copy. (Copy means the file will be copied without change.)

emit

Emit created climb to build directory.

```

create

Create a new Airflow workflow.

Get the current parameters of a workflow. Request the current state of a workflow. Trigger the execution of a workflow. Optional update of workflow parameters for  $\hookleftarrow$

Copyright EVEREST Consortium, licensed under the Apache License 2.0. For contact and more details, please visit: https://everest-h2020.eu

Listing 1 – CLI of the everest basecamp tool. The cli is a wrapper of the python API, discussed in Section 6.

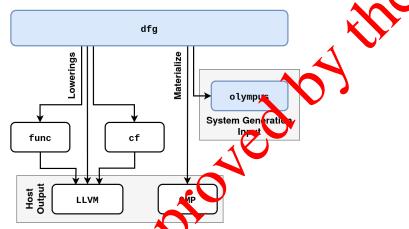

As will be described in this document, the compiler infrastructure for the different workloads, the integration, and assembly, as well as the interfacing to HLS tools are handled, for the most, within a common framework implemented in MLIR (see, for instance Figure 8). This effectively contributes to the *unification* of methods, which was one of the original goals of the EVEREST SDK to enable the convergence of data-centric applications involving HPC, Big Data, and machine learning.

Figure 2 – Basecamp, an interface to interact with the complation flows in the EVEREST SDK.

This deliverable describes the final design of the ASL in Section 3. We describe the adaptations to the Ohua DSL to cater for implicit dataflow applications, the the routing algorithm described in Deliverable D2.1, with extensions to support hardware offloading, the basic Cfdlang DSL for tensor kernels in HPC, like in Computational Fluid Dynamics (CFD) applications in Deliverable D2.1 and new abstractions to support the expressions identified in the radiation module of WRF; and how we leverage the prominent TVM framework for machine learning for decision-making in multiple use cases as described in Deliverable D2.1.

The MLIR-based intermediate languages to support the different workloads in the EVEREST project are described in Section 4. This introduces novel frontend dialects, intermediate dialects for generalized Einstein notation, dataflow and system and Integration as well as for custom number representations. Section 4 also describes transformations and lowering passes within the MLIR stack. This includes typical coarse-grained optimizations for dataflow argustaic and polyhedral optimizations for mathematical kernels in HPC, and standard optimizations for deep neural networks. Software-only versions can be produced after the optimization that can run on standard CPU nodes. Multiple such versions can be passed to the mARGOt autotuner for further optimization at runtime.

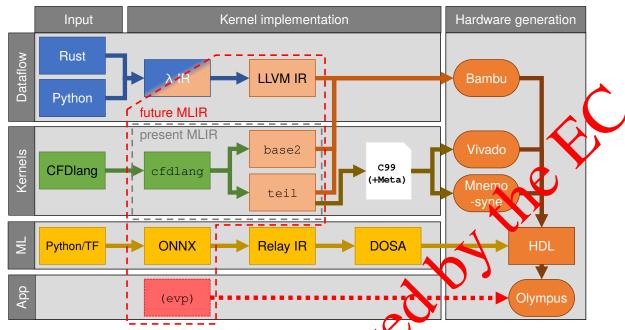

For nodes with reconfigurable hardware, the compiler middle-end can produce different interfaces and descriptors for the hardware generation part (*HW and HLS* in Figure 1). From the Rust backend of the dataflow language, LLVM IR can be generated for the Bambu HLS tool. For the HPC kernels, the compiler can interface directly via MLIR or LLVM with Bambu, or generate C/C++ code with HLS pragmas for Vitis/Vivado or Bambu. All this process is orchestrated and handled by EVP (see Figure 2). Machine learning applications are processed within the DOSA framework. The DOSA framework intelligently selects the best implementation for the operators used in the deep neural network. After this phase, multiple different Register Transfer Level (RTL) implementations for standalone kernels, functions (nodes in the dataflow graph) or machine learning operators are generated via HLS using either Bambu or Vivado/Vitis.

The final phase of the compilation framework (code-gen and system generation in Figure 1 is responsible for creating the entire system on the FPGA(s), performing the HW-SW integration and finally generating the binaries and bitstreams. This system-level generation is handled by Olympus (see Figure 2) as will be described in Section 5. Olympus also performs several optimizations to effectively use the FPGA resources and balance computation and communication time (especially relevant for systems with multiple memory channels). It also allows for the integration of kernels generated with different flows (e.g., different HLS tools or manual RTL blocks), enhancing the interoperability of the whole SDK. If an application requires more than one network-attached FPGA node, DOSA and the ZRLMPI tool handle the system generation. Here, the inter- and intra-FPGA communication is derived and optimized, and the FPGA design is generated. Links to the main tools of the compilation framework can be found in Table 1. For the final release, tool names and paths may change.

| Tool          | URL                                               |

|---------------|---------------------------------------------------|

| DOSA          | https://github.com/cloudFPGA/DOSA                 |

| ub            | https://github.com/KFAFSP/ub-mlir                 |

| base2         | https://github.com/KFAFSP/base2-mlir              |

| cfdlang       | https://github.com/everest-h2020/messner          |

| Ohua/Condrust | https://github.com/ohua-lang/condrust             |

| dfg-mlir      | https://github.com/Feliix42/dfg-mlir              |

| Bambu         | https://github.com/ferrandi/PandA-bambu           |

| Olympus       | https://github.com/StephanieSoldavini/olympus     |

| basecamp      | https://github.com/everest-h2020/everest_basecamp |

Table 1 – Links to main open source tools in the compilation flow

### **3 Language Support**

As specified in the project plan, Deliverable D4.1 and Deliverable D4.2, the EVEREST SDK provides support for kernels in HPC, machine learning and dataflow computing. This section describes the final versions of the languages, building on the preliminary versions described in Deliverable D4.2. This section also explains how the languages integrate within the use cases (with further details in Deliverable D6.3).

### 3.1 EVEREST Kernel Language

In Deliverable D4.1, we chose the CFDlang language [36] as the starting point for the EVEREST HPC workflow. This DSL was originally designed for CFD applications and later extended for cross-domain tensor expressions in [42]. It was chosen for its modeling of regular linear algebra, providing the freedom needed to implement data management techniques as described in Deliverable D3.1.

In Deliverable D4.2, we detailed how CFDlang and other DSLs can be integrated into an MLIR complex stack for rapid prototyping and language design. Moving to MLIR, the EVEREST HPC workflow is carried a composition of a separate DSL front-end and a reusable domain- and target-specific middle-end. In audition, we reported on extensions to the CFDlang language that we deemed necessary to support the computational motifs identified within RRTMGP [27]. These included richer index expressions, but also use the cannotations to specify non-functional requirements (e.g., quantization) for our pipeline to use.

As described in Deliverable D6.3, RRTMGP became our final target application for the EVEREST HPC workflow. RRTMGP is a state-of-the-art implementation of the correlated k-distribution (CKD) algorithm to solve the gas optics problem required to calculate atmospheric radiative transfer. Focusing on the short-wave bands only, this means that EVEREST ultimately targets the 4 kernels of interpolation, minor- and major absorber contributions, and Rayleigh scattering. To implement them, we derived the EVEREST Kernel Language (EKL) DSL from our earlier CFDlang prototype, with EKL now being our final version of the EVEREST DSL.

In terms of language and middle-end features, the above kerners demand support for in-place construction, broadcasting, index re-association, and subscripted subscripts. Figure 3 shows an example of the mathematical expression and the corresponding DSL snippet for the major absorbers kernel. The given expression approximates how the local gas concentration of two key species ("flavor") causes their broadened absorption lines to impact transmission. A key feature of the expression is the subscript-of-subscript into the tabulated distributions (dependent on thermodynamic state  $\chi$  and  $\chi$ ) and linear interpolation in 3 dimensions ( $\chi$  and  $\chi$ ). This example highlights some features of the DSL trait make it vastly more concise and easier to optimize than the old RRTMG Fortran implementation.

- Purity: Programs in EKL are pure, which means that expressions have no side-effects. This is closely related to their mathematical formulation, and leaves the compiler open to solutions that make clever use of memory. In the language, this is reflected through the let binding primitive, which supports scoping and shadowing (see line 3)

- Implicit loops: Including explicit loops, EKL programs are based on tensor primitives or index-metavariable expressions. This ensures that order dependencies are conscious decisions by the programmer and leaves the loop structure maximally open for implementation. Going further, Fortran's element-wise function opt-in is replicated, allowing those with scalar signatures to be implicitly applied to a tensor (note line 5).

- Einstein Summation Notation (ESN) The well-known ESN [21] allows tensor expressions that include reductions over known rings to be written naturally and concisely. This transforms tensor expressions into scalar expressions, which describe how individual result elements are produced. Using ESN, reductions prone to inadvertently inhibit compiler optimization are natural and safe (see line 9 ff.)

In the legacy RRTMG implementation, the kernel equivalent to line 9 is distributed over around 300 lines of Fortran code, spread across the 14 band functions. Some of this code is shown in Figure 4 for a direct

$$\tau_g^M = \sum_{dT} \sum_{dp} \sum_{d\eta} n_{\sigma_x,x,d\eta} \alpha_{\sigma_x,x,dT,dp,d\eta} k_{\overline{T}+dT,\overline{p}+dp,\overline{\eta}+d\eta,g}$$

Figure 3 – Example code in EKL.

Figure 4 – FRTM'G code snippet in Fortran.

comparison with the conciseness of the policy meaningful comparison is almost impossible due to this well-known shortcoming of the legacy code. Although the more modern RRTMGP implementation eliminates much of this code duplication as well, it is still an order of magnitude longer than the EKL implementation.

## 3.2 Fortran Integration for WRF

In Deliverable D4.2, we described how a DSL such as EKL can be embedded into an existing legacy application by mimicking the host language. In particular, we were referring to how CFDlang can integrate into Fortran by syntactically allowing the array definitions to be copied, thus eliminating indexing and Application Binary Interface (ABI) issues. Our goal was to establish a Fortran Foreign Function Interface (FFI) layer that would allow embedding the DSL directly into Fortran, and compiling using a preprocessing step.

As outlined in Deliverable D6.3, this approach turned out to be infeasible due to unsolvable ABI issues with Fortran, the structure of the legacy RRTMG implementation, and the subsequent switch to RRTMGP. To obtain a workable and easily maintained implementation, an ABI has to be frozen manually, unless massive scope creep at the level of WRF modularization is acceptable. We came to this conclusion also after consulting experts in the field, including the authors of RRTMG (and RRTMGP, for that matter).

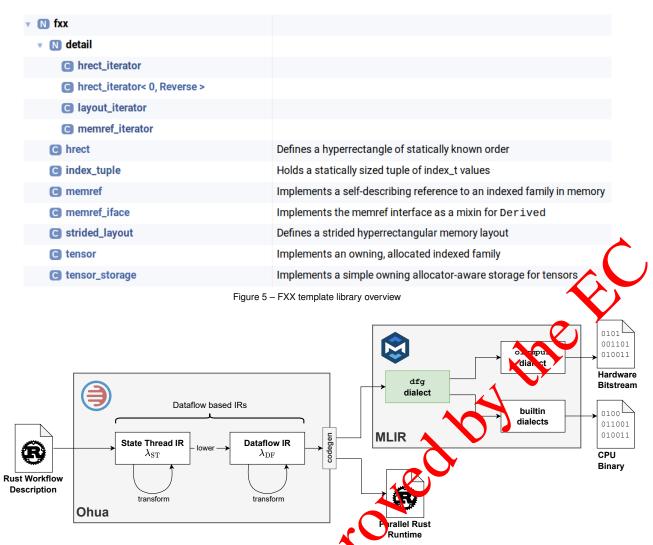

Nevertheless, solid FFI is still required between MLIR and C++, the latter of which being the language

Figure 6 – Current status of the Ohua/fordrus and dfg compilation flow.

we wrote the WRF plug-in in. While solutions exist we provide a more modern C++20 wrapper that facilitates using memref primitives as introduced by MLIR (see Figure 5). This effectively trivializes the inclusion of kernels code-generated via MLIR, pinned to some ABI for subsequent linking into the application, which is the main practical use of any currently feasible companion DSL compiler.

### 3.3 Dataflow: Ohua Condust

As basis for a language that can express dataflow, we use the Ohua compiler framework [10, 9]. An earlier prototype of the framework used its own frontend DSL that closely resembled the host language, but differed in the supported language features and the grammar definition [46]. The current version of the language, instead, uses a subset of the host language as input (e.g., Rust and Python). This allows the easy reuse of existing code, which significantly improves the usability of Ohua, one of the key requirements defined in Deliverable D2.2. More importantly, it also allows for quicker compiler extensions to support new languages. We can use existing parser and Abstract Syntax Tree (AST) definitions in both the front-end for parsing and the back-end for code generation. The current description of the syntax and the semantics of the language can be found in [41], with a more modern version of the language called **Condrust**. The compilation flow described in Deliverable D4.2 is now updated as shown in Figure 6.

An Ohua/Condrust program is a composition of calls to both stateless and stateful functions in a separate file, making it a formal coordination language. As described in Deliverable D4.2, the programming model imposes restrictions, some beneficial to safety and ease hardware-software designs. Most notably, passing by

reference is prohibited, and programs follow a strict move semantics. This means that all dataflow dependencies become visible in the program and thread-safety can be ensured.

A key motivation behind using a dataflow-driven DSL in the EVEREST project is that a Dataflow Graph (DFG) abstracts over the individual computations that form the algorithm. This comes in handy when deploying such a program onto heterogeneous architectures using the dfg MLIR dialect. The abstraction allows for a tight integration for off-loading single nodes of the DFG to FPGAs using HLS, as outlined in Section 5. Since the off-loaded functions themselves are not part of the compilation process, the main difference between offloaded functions and normal functions is the communication with the nodes. Normal nodes of the DFG communicate with one another using FIFO queues, both in the parallel Rust runtime as in the parallel MLIR generated runtime. Communication with an off-loaded node, however, requires actual data transfers from and to the accelerator. Furthermore, not all data-flow transformations provided by Ohua/Condrust can be trivially applied to code running on hardware, such as parallelization. To notify the Ohua Compiler (ohuac) of this change, functions that will be deployed onto the FPGA are annotated with a macro:

```

#[kernel(offloaded = true, multiplicity = [1, 1, 1], path = "projection.cpp")]

let cv: CandiVector = projection(gv, mapcell);

```

The offloaded flag allows the simple toggling of the offloading of a node in the graph. All additional information in the annotation is required by down-stream tools of the EVEREST SDK, namely *Offinpus*, as will be explained in Section 4.3 and Section 4.5.

An implementation of the *Map Matching* algorithm from the Traffic Simulation Use Use, would then look like this:

```

fn match_one(gv: GpsVector, mapcell: MapCell) -> RoadSpeedVector {

#[kernel(offloaded = true, multiplicity = [1, 1, 1], path = "projection.pp"]

let cv: CandiVector = projection(gv, mapcell);

let t: Trellis = build_trellis(gv, cv, mapcell);

let rsvbb: RoadSpeedVector = viterbi(t, cv);

interpolate(rsvbb, mapcell)

}

```

### 3.4 Machine Learning

With respect to language support for Machine Learning (ML) no fundamental changes were applied to the compilation flow described in Deliverable D4.2. This is mainly due to fact that ML frameworks and the community-standard Open Neural Network eXchange (NNX) [43] specification used in EVEREST are mature and have remained stable. Recently, the ML flow also supports torchscript [6] as input language, besides ONNX. The support of torchscript improves the connection to the community framework Pytorch, which is used to develop and train DNNs. Also, the support of torchscript allowed the integration of post-training quantization (PTQ) via the open-source tool brevitas [22].

### 4 Intermediate Representations and Transformations

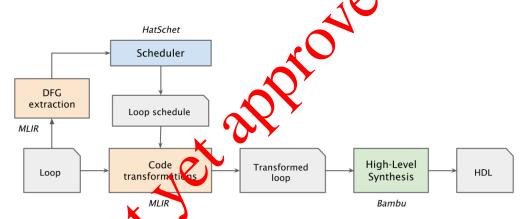

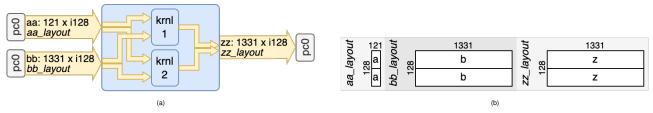

Figure 4 in Deliverable D4.2 sketched the status of the intermediate representations in the project in the alpha release (replicated in Figure 7 for better readability). The figure captured the concerted effort to achieve unification at the level of the intermediate representations. Apart from a frontend for Ohua/Condrust and integration of ML applications, an important missing component was an end-to-end integration with Olympus for system-level design.

Figure 7 – IR status and plans in Deliverable D

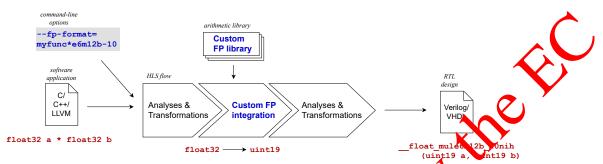

Today, the MLIR stack of the EVEREST SDK is much more complete as depicted in Figure 8. This design follows the design rationale described in Deliverable D4.2. As shown in the figure, external frontends can generate representations to enter the EVEREST SDK like torch and tosa. ML applications from TVM can be read into the jabbah dialect. To converge and ostimize the different DSLs for ML, we follow the concept of Operation Set Architectures [30]. This level of austraction, captured by jabbah, is also used to optimize the distribution of ML applications [34]. The SDK provides dialects for the frontends of the kernel language (ek1), the coordination language (dfg), and the legacy CFDlang (cfdlang). The dialects ek1 and cfdlang can be lowered to an MLIR implementation of the intermediate tensor language [35] (teil) and a new dialect for the Einstein notation (esn) described in this section.

Custom data representations are often needed to truly exploit the efficiency of hardware implementations. To this end, the SDK includes a set of dialects to properly model custom data types in MLIR[13], namely, base2, cyclic, bit and the The latter is being moved to core MLIR for proper support for undefined behavior. The remaining dialects handle integration within the EVEREST platform (evp) and system-level optimization based on the dataflow of the application (olympus). Both are highly relevant for the hardware generation flow described in Section 5.

In previous deliverables, we have provided details about dialects such as base2, tei1, and cfdlang. In this section, we focus on the new dialects ek1, esn, dfg, evp, and olympus. While most target- and domain-specific optimizations have been described in Deliverable D4.2 and our corresponding publications, this last phase increased the technical complexity of our MLIR dialegt stack. As a result, additional utility transforms were introduced, which we mention in the following whenever they become relevant.

Figure 8 – EVEREST MLIR dialects (in blue) and their integration with other core MLIR dialects (green). Dialects under construction in greatly luce.

#### 4.1 ekl

In Section 3.1, we described how the EKL is designed and what features its front-end possesses. This is realized using the ekl dialect, which is an MLIR implementation of the EKL front-end analogous to what was previously reported in Deliverable D4.2. In particular, ekl is an AST for EKL, as well as the IR that holds the result of expression elaboration during semantic analysis.

The ekl dialect is directly based on cfdlang, which means that it modes the syntactical structure of an EKL program. Conceptually, an ekl program is compiled into an accelerator by simplifying expressions, deciding on tensor storage and lifetime, and then implementing the resulting side effecting expressions. In Deliverable D4.2, we briefly described the canonicalization and expression implementation steps required. In addition to cfdlang's features, the ekl dialect now also has first-class support for type-level annotations.

MLIR does not feature a dependently-typed type system. Cutting-edge MLIR-backed language implementations, such as Mojo and, to some extent, CIRCT, come with their own mock-up of dependent types. EKL also requires such a feature to implement the user-facing type annotations used to perform automatic Domain-Space Exploration (DSE) of scalar data types. As above in Figure 9, we decided to encode such constructs by representing types as values. Consequently, the MLIR types of ek1 operations are in fact only of syntactic nature, e.g., "any tensor".

Figure 9 - Example of EKL type constraints.

As a result, type checking on an ekl program has to be performed in a separate pass, which instantiates the SSA values representing the concrete types. The well-formedness of such a fully annotated program is verified using standard MLIR verifiers, which can then act fully locally. Another aspect related to type checking is the correctness of subscripting and consistent use of index-metavariables. This is mostly left to the esn dialect, which ekl expressions translate to.

#### 4.2 esn

In Section 3.1, we described a new feature of EKL, which is its ability to represent expressions in ESN. An ESN expression is a type of tensor expression that is based on index-metavariables and simplifies reductions over

known rings.

Let A, B denote values of  $\mathbb{R}^2$ . The matrix-matrix product C = AB is given by the the following ESN expression

$$\mathbf{A}_{ik}\mathbf{B}_{kj}\tag{1}$$

By convention, an index appearing only once is *bound*, and an index appearing exactly twice is a *reduction*. In our example, the indices i and j are bound, and k is a reduction. The shape of the result of an ESN expression is implied by the domains of the bound indices in the order they appear in. We can make this explicit by turning the expression into an assignment

$$\mathbf{C}_{ij} = \mathbf{A}_{ik} \mathbf{B}_{kj}$$

The indices i, j, k vary over the result elements, and are therefore *local* to the expression. An arbitrary but fixed parameter is called a *free* index, and must be distinguished from the local indices. The reduction in k can be made explicit to resolve this issue

$$\mathbf{C}_{ij} = \mathbf{A}_{i[\underline{k}]} \mathbf{B}_{\underline{[k]}j}$$

$$= \sum_{k} \mathbf{A}_{ik} \mathbf{B}_{kj}$$

By convention, the domain of a local index is implied by *all* of its subscript uses. This means that every domain implied by an operand subscript must be congruent for a given local index. Also, subscript index arithmetic is not allowed. An ESN expression involving a reduction implies some commutative semigroup, it follows that the order of reductions is irrelevant and that scalar-associative ESN expressions are also tensor-associative. In general, ESNs are used when there is an unambiguous semiring defined over the involved scalars.

We implemented an MLIR dialect called esn that represents ESN expressions. An example program is provided in Figure 10. Its primary purpose is to make tensor expressions accessible to scalar arithmetic transformations, a strong point of ESN. Since ESN expressions imply parallelist, and regular loops, esn also serves to estimate and reduce both complexity and memory. Finally, esn provides a more convenient intermediary for a front-end lowering path due to its implied shapes.

The esn dialect features an elaboration step that "type checks" the index-metavariables involved in the expression. This makes it able to work with dynamically cized tensors, while still eagerly checking static correctness. This feature is used by the ek1 front-end, to elaborate the user expressions, which do not involve the dimensions. Although this system could be extended for non-congruential index geometries, this is not part of the ESN, and we were unable to find any uses for, e.g. affine indexing.

### 4.3 dfg

The dfg dialect has been designed to express KPN-style dataflow graphs with heterogeneous node placement. It can be generated from a more high-level graph representation, as outlined in Section 3.3. This can then leverage some of the dataflow transformations described in Deliverable D4.2. However, dfg also features a custom syntax which ellows users to even ergonomically express a graph directly using the dialect.

The dialect consists of the types and primitives necessary to model the two main components of a data flow graph: *nodes* (i.e., encapsulated library functions provided by the developer), and *edges* (i.e., FIFO communication channels between the nodes). It provides a dfg.operator op to define the semantics of the nodes and dfg.instantiate to instantiate the operator as a node in the graph. For streaming semantics, dfg.loop provides a way to loop operator execution until connections are closed. The dfg.channel operator creates two connected dfg.input and dfg.output values. These can be used within an operator to move data to and from the channels using dfg.push and dfg.pull. Offloaded kernels can be marked as such when instantiating an dfg.operator.

A complete example of an algorithm expressed in the dfg dialect can be seen in 1. It shows a graph constructed from three nodes, sum, get\_op and pow2. The latter is offloaded onto hardware, the sources of which reside in the specified file. The sum node runs in a loop, streaming new inputs.

```

dfg.operator @sum inputs (%op_a: ui32, %op_b: ui32)

outputs (%a: ui32) {

dfg.loop inputs (%op_a: ui32, %op_b: ui32) outputs (%a: ui32) {

%inp1 = dfg.pull %op_a : ui32

%inp2 = dfg.pull %op_b : ui32

%result = arith.addi %inp1, %inp2 : ui32

dfg.push(%result) %a : ui32

}

}

dfg.operator @get_op outputs (%op_b: ui32) {

%b = func.call @get_op() : ui32

dfg.push(%b) %op_b : ui32

}

dfg.operator @pow2 inputs(%op_c_in: ui32) outputs(%op_d_out: ui32)

attributes { evp.path = "src.cpp", multiplicity = array(14:),

// algorithm entry point

func.func @run_dfg(%op_a: ui32) -> ui32 {

%op_a_in, %op_a_out = dfg.channel() : ui32

%op_b_in, %op_b_out = dfg.channel() : ui32

%op_c_in, %op_c_out = dfg.channel() : ui32

%res_in, %res_out = dfg.channel() : ui32

// inputs

dfg.push(%op_a) %op_a_out

dfg.instantiate @get_op outputs(%op

dfg.instantiate @sum inputs(%op_4

%op_b_in) outputs(%op_c_out)

// kernels seamlessly integrate

dfg.instantiate offloaded @pow2 inputs(%op_c_in) outputs(%res_out)

%res = dfg.pull %rea

return %res : ui3

}

```

Listing 1 – A complete example of an algorithm implemented in the dfg dialect.

```

%C = esn.let [%i, %j] : f64 {

%c1 = index.constant 1

%k = reduction

%dimA_1 = tensor.dim %B, %c1 : tensor<8x?xf64>

%A_ik = subscript %A[%i, %k] -> f64

%dimB_1 = tensor.dim %B, %c1 : tensor<3x?xf64>

%B_kj = subscript %B[%k, %j] -> f64

%C = esn.let [%i, %j] : f64 {

%C_ij = arith.mulf %A_ik, %B_kj : f64

%k = reduction

yield %C_ij : f64

upper_bound(\%i) = 8

} reduce (%lhs, %rhs) {

%pi = to_index %i

%sum = arith.addf %lhs, %rhs : f64

upper_bound(%k) = %dimA_1

yield %sum : f64

%pk = to_index %k

}

A_ik = subscript A[(\pi), (\pi)] :

→ tensor<8x?xf64>

upper_bound(%k) = 3

(a) Domain-implicit form

upper_bound(%j) = %dimB_1

%pj = to_index %j

B_kj = subscript B[(%pk), (%pj)] :

→ tensor<3x?xf64>

%C_ij = arith.mulf %A_ik, %B_kj

yield %C_ij : f64

} reduce (%lhs, %rhs) {

%sum = arith.addf %lhs, %rhs

yield %sum : f64

```

A data flow graph runtime described by this dialect spawns all instantiated nodes of the graphs with their connections in place. All nodes execute in parallel, the blocking channel symmetries ensuring an efficient use of computing resources during execution. When an operator terminates all used input and output channels will be closed. Operators that are internally using a dfg.loop will be effected in an endless loop until one input or output channel is broken, i.e., the other end of the channel is missing. If that happens, the operator terminates immediately, not processing any further input and instead triggering all linked nodes to terminate execution, too. This ensures that the runtime cannot get stuck in an endless loop without further data.

Figure 10 – esn program for eq. (1)

Non-looped operators are used, for instance, to capture environment variables that are injected into the graph. This usually includes the initial inputs to the computation, ensuring the computation pipeline shuts down after processing all inputs.

For offloaded nodes, a wrapper will be generated for the host-side driver of *Olympus*, which will be explained in Section 4.5.

Other dialects that provide abstractions for this Model of Compute (MoC) exist, most notably the handshake dialect [19] from the CIRCT project. However, this abstraction is not usable for the EVEREST project, as it has been designed for use in hardware generation and, therefore, uses the handshake protocol for data exchange, which is not necessary here. Turthermore, it uses implicit FIFO channels, giving users no explicit control over their use and sizing, which is an integral part of the abstraction provided through dfg.

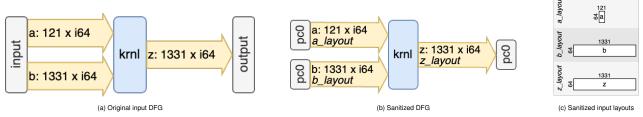

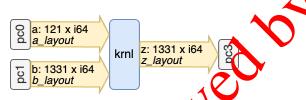

#### 4.4 evp

The evp dialect is a dialect that, looking forward, will represent high-level connections between software and hardware components for heterogeneous deployments. Its operations assist in relocating nodes of dataflow graphs across heterogeneous compute devices. It is used by the evp tool, which can be seen as the equivalent of what a linker is in traditional software deployments. More information will be provided in Section 6.2 in the context of the final code generation flow of the SDK.

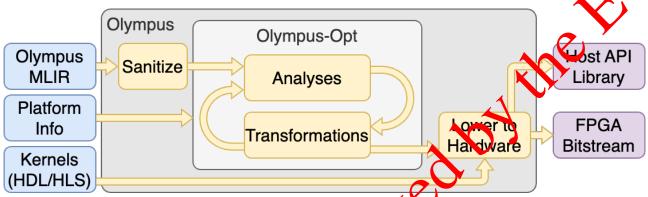

#### 4.5 olympus

#### Kernel operator

Return: void (Any outputs are the last parameters)

#### Attributes:

callee : The name of the kernel implementation (C function, Verilog module, etc)

latency, ii: Timing estimates (latency, initiation interval) from kernel HLS/synthesis

ff, lut, bram, uram, dsp: Resource estimates from kernel HLS/synthesis

operand\_segment\_size: Defines which parameters are inputs and outputs. (In this example, the '2' in index 0 means the first two parameters are inputs. The '1' in index 1 means the next 1 parameter is the output.)

path: Where to find the kernel implementation file.

Parameters: The inputs and outputs as determined by operand\_segment\_tize. Either scalar data of primitive types or olympus.channel types. In the same order as in the kernel implementation.

#### Channel operator

```

%2 = "olympus.channel"() {

paramType = "stream",

depth = 20

} : () -> (

!olympus.channel<i32>

```

Return: The channel, to be used as input/output operands in kernel operators.

#### Attributes:

persistent: (optional, default: Take) Boolean. If true, this data is transferred between the host and HBM/DDR once during initialization. An olympus index can be associated in order for the kernel to use different portions per iteration.

paramType: describes the properties of the data in one of three ways:

- "stream": Must be produced and consumed in the same order and consist of small, statically sized elements.

- "small": Can be random access, but in total the data needed for a single kernel iteration should be at most on the scale of 100s of kB and be organized of simple structures without nesting or indirection.

- "complex": Can be anything: huge, random access, have indirection, and/or be constructed of nested structures.

depth: Describes how large the data is in total. If paramType==stream, depth is the maximum necessary channel depth. If paramType==small, depth is the number of elements. If paramType==complex, depth is the number of bytes.

#### Channel type

!olympus.channel<i32>

*Type parameter:* A signless integer of arbitrary bitwidth. The interpretation of the data is not important, only the width. Therefore, a 32-bit float, a fixed-point value with 10 integer bits and 22 fraction bits, and a 32-bit integer should all be represented as 'i32'.

#### **Index operator**

```

%2 = "olympus.index"( %2 ) {

depth = 4

} : (

!olympus.channel<i32>

) -> ()

```

Return: void

Attributes:

depth: Describes how large the data needed for one iteration is. It should be a factor of the depth the associated persistent channel.

Parameters: The associated channel. The value of the index along with the depth (used as a stride) will be used to select a portion of the data from this channel for transferring between HBM/DDR to the kernel.

#### Index type

!olympus.index<i32>

*Type parameter:* The type of the scalar value used as an index.

One advantage of this flow is that it directly enables us to target CPUs, and also puts graphical processing units (GPUs) in range of future extensions. As an example, Figure 11 shows the inverse Helmholtz operator kernel in the cfdlang dialect in MLIR, next to an excerpt of its LLVM IR swering. This lowering is obtained using standard MLIR components directly from the bottom of our dialect blerarchy and can be processed with LLVM optimizers for targeting many different CPU architectures.

```

ant_11x11x11xf64 = private constant [11 x [11 x [11 x double↔] zeroinitializer

8 * @malloc(i64)

void @free(i8 *)

efine void @kernel(double* %0, double* %1, i64 %2, i64 %3, i64 %4, \leftrightarrow i64 %5, i64 %6, double* %7, double* %8, i64 %9, i64 %10, i64 %0, %11, i64 %12, i64 %13, i64 %14, i64 %15, double* \leftrightarrow %17, i64 %18, i64 %19, i64 %20, i64 %21, i64 %21, i64 %22, i64 %23, i64 \leftrightarrow %24, double* \leftrightarrow %26, i64 %27, i64 %28, i64 \leftrightarrow %29, i64 \leftrightarrow %30, i64 \leftrightarrow 31, i64 %31, i64 %32, i64 \leftrightarrow 33) { w35 = call dereferenceable_or_null(10648) i8* @malloc(i64 10648) br label %37

cfdlang.program {

cfdlang.input @S

cfdlang.input @D

cfdlang.input @u :

cfdlang.define @t :

%0 = cfdlang.eval

%1 = cfdlang.eval

%2 = cfdlang.prod

%3 = cfdlang.cont

; preds = %63, %34

%38 = phi i64 [ %64, %63 ], [ 0, %34 ]

%39 = icmp slt i64 %38, 11

br i1 %39, label %40, label %65

%4 = cfdlang.prod

%5 = cfdlang.cont

indices [2 5]

%6 = cfdlang.prod

%7 = cfdlang.cont

cfdlang.yield %7

11] indices [2 5]

40:

br label %41

; preds = %37

cfdlang.define @r : [1

41:

%42 = phi i64 [ %62, %61 ], [ 0, %40 ]

%43 = icmp slt i64 %42, 11

br i1 %43, label %44, label %63

; preds = \%61, \%40

br label %45

; preds = %48, %44

45:

%46 = phi i64 [ %60, %48 ], [ 0, %44 ]

%47 = icmp slt i64 %46, 11

br i1 %47, label %48, label %61

1^{48:} \\ \%49 = \text{mul } \text{i} 64 \ \%38, \ 121 \\ \%50 = \text{mul } \text{i} 64 \ \%42, \ 11 \\ \%51 = \text{add } \text{i} 64 \ \%49, \ \%50 \\ \%52 = \text{add } \text{i} 64 \ \%51, \ \%46 \\ \end{cases}

```

Figure 11 – Example lowering from cfdlang to LLVM-IR (excerpt).

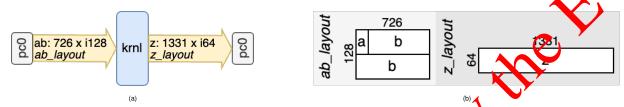

### deep neural network import e.g. from ONNX build abstract syntax tree (AST) (selected) optimizations %1 = conv2d(%0, %w0, %b0, kernel=(5,5), padding=0, layout=NCHW) %2 = relu(%1) %3 = max\_pool2d(%2, kernel=2, stride=2) %4 = conv2d(%3, %w1, %b1, kernel=(3,3), padding=0, layout=NCHW) (simplified print of AST) lowering operation set {%1, %2} map operation set {%3, %4} to hardware-specific instructions to template building blocks (i.e. store parameters in memory) (i. e. integrate parameters as constants) (3b) "execute" operations "execute" operations (3a) as instruction for an xPU as IP core instantiation Processing Unit / Engine Control Unit Matrix Unit On-Chip DRAM/HBM Management (4a) FPGA with engine-type accelerator (4b) FPGA with streaming-type accelerator

Figure 12 – Basic principle of the Operation Set Architecture (OSA). An operation can be executed either by lowering it to an instruction (for engine-type accelerators, left-hand side) or by implementing it as parameterized hardware IP conformation of the operation of the Operation (Figure 12 – Basic principle of the Operation (for engine-type accelerators, right-hand side).

### 4.6 Connecting to HLS

As discussed in Deliverable D4.2, we guide HLS at a low-level abstraction, such as polyhedral descriptions in the affine dialect. During our higher level MLR transforms, we can establish resource estimates in terms of memory bandwidth. On the polyhedral level, we use this to reschedule sub-kernel regions for HLS, inserting annotations. This means that we output vendor-specific pragmas, such as Xilinx's #pragma HLS <?>, into an interchange format, such as C91. Flows with better MLIR integration, such as Bambu, remove the interchange format in favor of passing this information directly in MLIR. As discussed in Deliverable D4.2, we retain the possibility of generating different variants of a kernel or function. This is enabled by expression rewriting and different polyhedral schedules (to generate different pipelines with intermediate buffers). These variants can be used for runtime selection.

### 4.7 Machine Learning Abstractions and Optimization

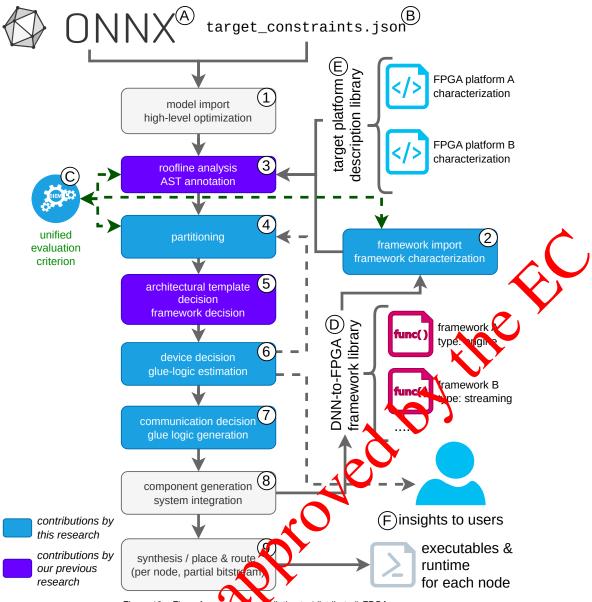

The ML flow to compile Deep Neuronal Networks (DNN) to FPGAs is implemented in the tool DOSA [28] using Operation Set Architectures [31]. In the following, we report on considerable progress with respect to the status from Deliverable D4.2.

#### 4.7.1 Operation Set Architectures

The FPGA community has been researching the implementation of neural networks on FPGAs for nearly 30 years, resulting in a *Cambrian explosion*[12] of DNN-to-FPGA tools<sup>1</sup> that scale from Edge to Cloud and target a wide variety of applications. Despite this variety, the architectures generated by all these existing frameworks can be sorted into two categories: **Engine-type** and **streaming-type** architectures, as depicted in the lower half of Figure 12.

The engine-type (see 4a) in Figure 12) consists of one or multiple custom-designed processing units (i.e., engines) that can execute domain-specific instructions and are often referred to as *NPU* or *xPU*. These processing engines frequently contain dedicated units for matrix multiplication, vector processing, and non-linear functions, since these are the mathematical foundations of today's DNNs. Consequently, a DNN is broken down by a compiler into instructions that those processing engines can handle. These instructions are issued by a control unit at run-time and scheduled based on memory dependencies and processing unit availability. Although this pattern is simple, the design space is huge: For example, the processing elements can contain various specialized units with different data sizes or types. Examples of this type of architecture are TMA's VTA [18], Xilinx's Vitis AI [47] and Microsoft's Brainwave [12].

The streaming-type architecture (see (4b) in Figure 12) integrates all the application-specific operations in the FPGA logic, so that the data *just* streams through the fabric at run-time. This type of a chitecture can achieve a higher throughput with lower latencies at the cost of higher resource usage that the engine type. The design space of this template is also huge. Starting with data types of different precision per operation to a variety of unrolling of loop parallelisms and pipelining options. Example frameworks that generate this type of accelerators are hls4ml [8], Haddoc2 [1], and FINN [3].

Both architecture *templates*, streaming and engine, are well justified for different reasons. The streaming template is best used for DNNs that require high throughput and/or low latency. The engine-type accelerators are better for large DNNs in latency-relaxed environments or if there are insufficient FPGA resources to implement the streaming type.

Throughout the project, we advocated for deploying mixed architectures built upon a combination of specialized streaming- and engine-type accelerators.

To compare different mixtures of architecture templates and to combine them into optimal solutions, we propose the operation set architecture (OSA) principle. The levels of abstraction of these operation sets are selected to allow the compiler to make meaningful comparisons of performance and resource metrics between totally different implementations.

With respect to the intermediate representation (IR) snippet of an abstract syntax tree (AST) in Figure 12 1, the conv2d, re1u, and max\_poo12d constitute components of such operation sets. In essence, the operation sets are groups of those components. We selected this level of abstraction after we revisited the long list of specialized frameworks, existing domain specific languages (DSLs), IRs, and optimization techniques of existing tool flows for DNNs. We observed that compilers of frameworks that target engine-type accelerators apply the heaviest optimizations. This results from the fact that DNNs are compiled into engine-type instructions, for which well-known optimization methods from classical CPU and GPU compilers can be used. Such optimizations include constant including, dead code elimination, operator fusion, elimination of common sub-expressions, simplify paddings, and simplify the data flow graph for inference. Surprisingly, frameworks targeting streaming-type accelerators perform either no or only a few hardware-specific optimizations [1, 45, 49, 20] and even leave constant folding to the synthesis tools in most cases.

Therefore, we concluded that the level of abstraction for comparing different implementations should be chosen such that the decision between engine-type and streaming-type accelerators happens after these "basic" optimizations but before the program gets lowered further, since many of these optimizations would help the streaming-type accelerators, too. Following this path, the compiler can optimize a DNN graph above or at this level of abstraction (cf. 1) in Figure 12), detached from the lower-level details of the execution of one operation. This level is similar to the abstraction levels used by popular DSLs like RelayIR [18] [37] or ONNX [44]. Only after that, the compiler decides between engine and streaming implementations of each operation. Therefore, such a higher-level operation is either lowered to engine/NPU/xPU-specific instructions

or synthesized as a parameterized IP block for streaming accelerators. Engine operations are lowered into engine/NPU/xPU specific instructions (2a), and streaming operations are synthesized as a parameterized IP block (2b).

From an AST (1) point of view, all operations all operations are *somehow* available specialist frameworks, illustrated with the arrows (3a) and (3b). How the operations will be *executed* in detail is up to the different frameworks (cf. (2a) and (2b)). Thus, each of these frameworks supports different a *set of operations* through its chosen target architectures (cf. (4a) and (4b)). However, the AST can be optimized and transformed without considering these details. In the example of Figure 12, the first two higher-level operations, conv2d and relu, are executed on an engine-type accelerator, while the following two operations, max\_pool2d and conv2d, are then *executed* by implementing IP cores in a streaming way.

The method (1)—(4) of Figure 12 is what we refer to as "Operation Set Architecture", because it provides a meaningful unified abstraction level and utilities to compare and optimize different implementations of similar sets of operations.

## 4.7.2 DOSA: Distributed Operation Set Architectures using organic compiler principles

Our goal is to develop an *organic compiler* that analyzes a given DNN and selects the best possible template-type and implementation offered by several frameworks for each arithmetic operation of this DNN. This compiler should understand a conventional DNN exchange standard and provide the user with insights on achievable performance, possible bottlenecks, and how the user's constraints influence the architectural decision. The DSE by this compiler should also consider partitioning, with model- and a vice-parallelism as options. They should ideally take only a few seconds to allow frequent iterations and optimizations with a user in the loop. Therefore, this compiler must be able to predict performance and a source consumption for each possible implementation quickly and reliably and must use meaningful criteria to compare these estimates.

Figure 13 shows the flow diagram of our organic compiler. Such an organic compiler requires a DSE phase that can analyze the DNN and that knows about the characteristics of the available frameworks. Consequently, an organic compiler has four inputs: The DNN (A), sprcified in a community standard as, e.g., ONNX [43], the targeted performance and resource constraints (B) are description of the targeted devices (E), and the available specialist frameworks as library (D).

The flow starts ① with the import of the DN and the execution of straightforward optimizations, such as constant folding, dead code elimination operator fusion. Also, an AST of the DNN is built. In parallel, the library of specialist DNN-to-FPG frameworks ① and the library of available target platforms ② are imported ② and prepared for the DST ①.

In the next step ③, the characterizations of step ② are then used to annotate the AST of the DNN operation-wise using a roofline-live analysis, together with the library of available platform characterizations.

Afterward, having a detailed AST annotation, the DSE phase starts with partitioning the DNN (4), if required by the size or throughput requirements of the DNN. The partitioning is based on the roofline analysis and bandwidth analysis. Next, based on an updated roofline analysis and the estimated latencies between nodes, high-level architectural decisions are made (5). Foremost, this decision involves deciding if weights of the operations of the DNN can be stored in an off-chip memory or if it has to stay on-chip because the available bandwidth would not allow to load them fast enough (cf. [31, 28]). Also, the best available specialist framework that can implement the decided micro-architecture with the derived performance requirements is selected. Next, (6), if multiple target devices are available, the best candidates are selected in this step. This step also includes calculating the resources necessary for the *glue logic* between the selected accelerator blocks. Here, it could be that this glue logic consumes more resources that are left on some devices. In that case, this result is annotated, and the compiler continues with another partition step. After a valid solution is found, or if the compiler fails to find one, the user is informed about the resulting performance, resource footprints, and potential bottlenecks (F).

Figure 13 - Flow of an organic compilation to (distributed) FPGAs.

As the seventh step ⑦, the communication details between FPGA nodes are decided if the solution consists of multiple nodes. This involves finding the best synchronization pattern and deciding the type of serialization of multi-dimensional tensors. These decisions influence the latency between FPGA nodes only minimally since they are all implemented in a data flow architecture as part of the network stack of the FPGA logic. For the inter-node communication, DOSA builds on the ZRLMPI framework [33, 32].

### 5 Hardware Generation Flow