# dEsign enVironmEnt foR Extreme-Scale big data analyTics on heterogeneous platforms

# D4.2 — Intermediate report of the compilation framework

#### **Project Summary Information**

| Project Title           | dEsign enVironmEnt foR Extreme-Scale big data analyTics on heterogeneous platforms |

|-------------------------|------------------------------------------------------------------------------------|

| Project Acronym         | EVEREST                                                                            |

| Project No.             | 957269                                                                             |

| Start Date              | 01/10/2020                                                                         |

| <b>Project Duration</b> | 36 months                                                                          |

| <b>Project Website</b>  | http://www.everest-h2020.eu                                                        |

# Copyright

© Copyright by the EVEREST consortium, 2020.

This document contains material that is copyright of EVEREST consortium members and the European Commission, and may not be reproduced or copied without permission.

| Num.       | Partner Name                                                          | Short Name | Country |

|------------|-----------------------------------------------------------------------|------------|---------|

| 1 (Coord.) | IBM RESEARCH GMBH                                                     | IBM        | CH      |

| 2          | POLITECNICO DI MILANO                                                 | PDM        | IT      |

| 3          | UNIVERSITÀ DELLA SVIZZERA ITALIANA                                    | USI        | CH      |

| 4          | TECHNISCHE UNIVERSITAET DRESDEN                                       | TUD        | DE      |

| 5          | Centro Internazionale in Monitoraggio Ambientale -<br>Fondazione CIMA | CIMA       | IT      |

| 6          | IT4Innovations, VSB – Technical University of Ostrava                 | IT4I       | CZ      |

| 7          | VIRTUAL OPEN SYSTEMS SAS                                              | VOS        | FR      |

| 8          | DUFERCO ENERGIA SPA                                                   | DUF        | IT      |

| 9          | NUMTECH                                                               | NUM        | FR      |

| 10         | SYGIC AS                                                              | SYG        | SK      |

Project Coordinator: Christoph Hagleitner – IBM Research – Zurich Research Laboratory

Scientific Coordinator: Christian Pilato – Politecnico di Milano

The technology disclosed herein may be protected by one or more patents, copyrights, trademarks and/or trade secrets owned by or licensed to EVEREST partners. The partners reserve all rights with respect to such technology and related materials. Any use of the protected technology and related material beyond the terms of the License without the prior written consent of EVEREST is prohibited.

## **Disclaimer**

The content of the publication herein is the sole responsibility of the publishers and it does not necessarily represent the views expressed by the European Commission or its services. Except as otherwise expressly provided, the information in this document is provided by EVEREST members "as is" without warranty of any kind, expressed, implied or statutory, including but not limited to any implied warranties of merchantability, fitness for a particular purpose and no infringement of third party's rights. EVEREST shall not be liable for any direct, indirect, incidental, special or consequential damages of any kind or nature whatsoever (including, without limitation, any damages arising from loss of use or lost business, revenue, profits, data or goodwill) arising in connection with any infringement claims by third parties or the specification, whether in an action in contract, tort, strict liability, negligence, or any other theory, even if advised of the possibility of such damages.

## **Deliverable Information**

| Work-package        | WP4                                              |

|---------------------|--------------------------------------------------|

| Deliverable No.     | D4.2                                             |

| Deliverable Title   | Intermediate report of the compilation framework |

| Lead Beneficiary    | TUD                                              |

| Type of Deliverable | Report                                           |

| Dissemination Level | Public                                           |

| Due Date            | 01/10/2020                                       |

#### **Document Information**

| <b>Delivery Date</b> | 04/04/2022                                                                                                                                                                                                             |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| No. pages            | 41                                                                                                                                                                                                                     |

| Version   Status     | 0.4   Final                                                                                                                                                                                                            |

| Responsible Person   | Jeronimo Castrillon (TUD)                                                                                                                                                                                              |

| Authors              | Jeronimo Castrillon (TUD), Karl Friebel (TUD), Felix Wittwer (TUD), Burkhard Ringlein (IBM), Michele Fiorito (PDM), Fabrizio Ferrandi (PDM), Donatella Sciuto (PDM), Christian Pilato (PDM), Stephanie Soldavini (PDM) |

| Internal Reviewer    | Christoph Hagleitner (IBM)                                                                                                                                                                                             |

The list of authors reflects the major contributors to the activity described in the document. All EVEREST partners have agreed to the full publication of this document. The list of authors does not imply any claim of ownership on the Intellectual Properties described in this document.

## **Revision History**

| Date       | Ver. | Author(s)                 | Summary of main changes                                                   |

|------------|------|---------------------------|---------------------------------------------------------------------------|

| 12.01.2022 | 0.1  | Jeronimo Castrillon (TUD) | Initial structure                                                         |

| 17.03.2022 | 0.2  | Multiple contributors     | Major content in place                                                    |

| 18.03.2022 | 0.3  | Jeronimo Castrillon (TUD) | Finish overviews, simplified table of contents, fixed consistency issues. |

| 31.03.2022 | 0.4  | Jeronimo Castrillon (TUD) | Clean up, reacted to comments by internal reviewer.                       |

## **Quality Control**

| Approved by Internal Reviewer      | April 4, 2022 |

|------------------------------------|---------------|

| Approved by WP Leader              | April 4, 2022 |

| Approved by Scientific Coordinator | April 4, 2022 |

| Approved by Project Coordinator    | April 4, 2022 |

# **Table of Contents**

| 1 | EXECUTIVE SUMMARY  1.1 Structure of this Document                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5<br>5                                       |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| 2 | OVERVIEW OF THE COMPILATION FRAMEWORK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 6                                            |

| 3 | LANGUAGE SUPPORT AND INTERMEDIATE REPRESENTATIONS  3.1 Language Support  3.1.1 CFDlang Extensions  3.1.2 Fortran Integration for WRF  3.1.3 Dataflow  3.1.4 Machine Learning  3.2 Intermediate Representations  3.2.1 Design Rationale  3.2.2 Multi-Level Intermediate Representation (MLIR) Language Stack for Numerical Computations  3.2.3 Dataflow                                                                                                                                                                                         |                                              |

| 4 | <ul> <li>3.2.4 Machine Learning</li> <li>HIGH-LEVEL TRANSFORMATIONS AND DOMAIN-SPACE EXPLORATION (DSE)</li> <li>4.1 Kernel Transformations and Optimizations</li> <li>4.2 Dataflow Transformations and Optimizations</li> <li>4.2.1 Performance-Related Transformations</li> <li>4.2.2 Transformations for Offloaded Kernels</li> <li>4.3 Machine Learning</li> <li>4.3.1 Engine and Streaming type of Machine Learning (ML) architectures</li> <li>4.3.2 Leveraging Existing ML-tools for FPGAs</li> <li>4.3.3 DSE for ML Workload</li> </ul> | 19<br>19<br>20<br>20<br>21<br>22<br>22<br>22 |

| 5 | HARDWARE GENERATION FLOW  5.1 Hardware-Oriented Optimizations and Kernel Generation                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 26<br>27<br>28<br>29                         |

| 6 | CODE GENERATION AND RUNTIME INTEGRATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 35                                           |

| 7 | Conclusions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 37                                           |

| R | EFERENCES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 39                                           |

# 1 Executive Summary

The EVEREST project proposes a platform and system development kit to deploy demanding workflows to suitable high-performance or edge hardware [17]. This document provides an intermediate description of the compilation framework, midway through the project. The compilation framework plays a key role in providing high-level programming support for productivity together with a methodology for optimization. The latter includes software and hardware transformations as well as autotuning support for runtime adaptivity.

In this document, we describe the technologies, tools and components of the compilation framework. Details on how to use the tools are provided in Deliverable D4.3. The design presented here follows the specification provided in Deliverable D4.1, which depicted a complex landscape of programming languages (Fortran, Rust, C++, Python) and computational requirements (large workflows combining High-Performance Computing (HPC), Big Data and machine learning). In this document we describe the language abstractions, source-to-source high-level transformations and hardware-oriented transformations for computational motifs that are representative of those found in the use cases of the EVEREST project. Given the complexity of the use cases, some of which are further developed during the project, this document focuses on individual compilation flows and how they converge prior to execution on the EVEREST target platform.

## **Deliverable highlights**

| No. | Highlight                                                                                                                                                 | Section(s)                                  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|

| 1   | Coherent framework design, integrating multiple software components                                                                                       | Section 2<br>(Figure 1)                     |

| 2   | Language support for the different domains of the EVEREST project                                                                                         | Section 3.1                                 |

| 3   | Initial plan for convergent intermediate representation and optimization                                                                                  | Section 3.2.1,<br>Section 4.1<br>(Figure 4) |

| 4   | Infrastructure for transformation, optimization and variant-generation for the different domains of the EVEREST project                                   | Section 4                                   |

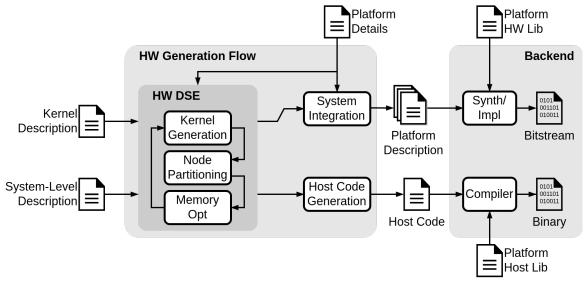

| 5   | Generalized HW generation flow with support for multiple downstream HLS-flows                                                                             | Section 5<br>(Figure 14)                    |

| 6   | Seamless connection between software compilation and hardware transformations for kernel-level optimizations, memory optimizations and system integration | Section 4.1-<br>Section 5.3                 |

| 7   | Initial integration with the runtime system                                                                                                               | Section 6<br>(Figure 21)                    |

#### 1.1 Structure of this Document

This document starts with an overview of the compilation framework in Section 2. The overview lists all involved software components of the framework, which are then described in the remaining sections. In particular, the added language support to react to the use case requirements Deliverable D2.2 is described in Section 3. The section also describes the compiler-internal representations and the interfacing to the hardware generation flow. Section 4 describes transformations and optimizations, leveraging the high-level intermediate representations introduced in Section 3. Hardware programming and integration flows are described in Section 5. This includes extensions to High-Level Synthesis (HLS) flows and system-level integration support for the EVER-EST platform. The presented flow is concluded with Section 6, which describes how the components in this document will be integrated with the dynamic runtime environment described in Deliverable D5.1. This deliverable finishes with conclusions and next steps in Section 7.

# 2 Overview of the Compilation Framework

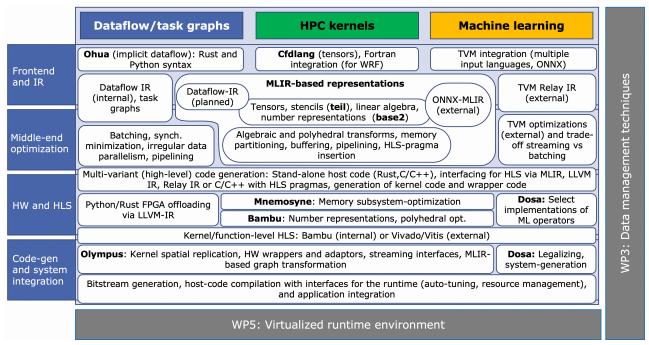

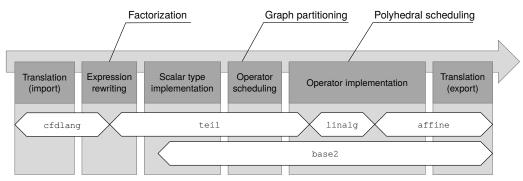

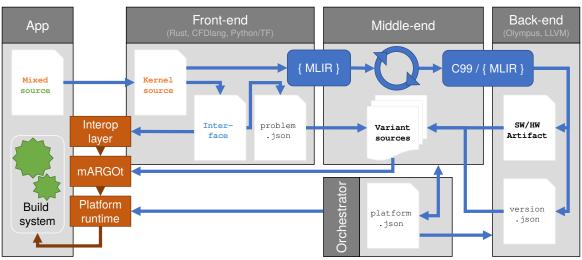

Figure 1 – Overview of the compilation flow.

Following from Figure 1 in Deliverable D4.1, a more detailed representation of the languages, components, tools, interfaces and methods of the compilation framework is shown in Figure 1. From the high-level point of view, the figure reflects the heterogeneity of the requirements identified early in the project. This is reflected on the multiple types of applications (dataflow/task graphs, HPC kernels and machine learning), the different languages (Fortran, C/C++, ONNX, Rust, Python and Domain-Specific Languages (DSLs)), the rich set of interfaces (via intermediate code in LLVM or MLIR, via generated C/C++ or Rust code and other metadata for variant generation), and the integration with multiple external tools and frameworks (WRF build system, TVM, the MLIR infrastructure, Vivado/Vitis HLS tools. As described in the proposal, one the goals of the EVEREST SDK and its compilation framework is to work on *unification* of methods, so as contribute to the convergence of data-centric applications involving HPC, Big Data and machine learning. At the intermediate level, Figure 1 shows unification around the MLIR framework. This is a considerable advancement with respect to the decoupled flows planed for simplicity in Deliverable D4.1. As the programming flows advance towards the HW of the EVEREST platform, the flows converge ending at the final bitstream and code generation step. For generality, the HW generation flow supports both vendor-tools (e.g., Xilinx Vivado/Vitis) as well as open-source alternatives (Bambu).

Figure 1 also shows that the data management techniques from WP3 inspire the implementations in the methods and tools developed within WP4. The code produced by the compiler can run standalone on the different nodes of the EVEREST platform, with only CPUs, or with bus or network-attached Field Programmable Gate Arrays (FPGAs). For final deployment, the code adheres to the Application Programming Interfaces (APIs) of the EVEREST runtime environment of WP5.

From top-to-bottom, the four major phases of Figure 1 are described in this deliverable. The language support (front end) and the internal compiler representations are described in Section 3. We describe the adaptations to the Ohua DSL to cater for implicit dataflow applications, like the routing algorithm described in Deliverable D2.1; the basic Cfdlang DSL for tensor kernels in HPC, like in Computational Fluid Dynamics (CFD) applications in Deliverable D2.1; and how we leverage the prominent TVM framework for machine learning, for decision making in multiple use cases as described in Deliverable D2.1. The MLIR-based intermediate languages support primarily the HPC kernels. However, as shown in the figure, we plan to provide a dataflow IR in MLIR, equivalent to the internal one used in the Ohua compiler. That way and with the ONNX-MLIR import a unified representation for all types of application classes can be readily obtained.

In the compiler middle end (optimization in Figure 1) the EVEREST compilation framework integrates a series of analysis and optimizations for the different application cases. This includes typical coarse grained optimizations for dataflow, algebraic and polyhedral optimizations for mathematical kernels in HPC and standard optimizations for deep neural networks. Software-only versions can be produced after the optimization that can run on standard CPU nodes. Multiple such versions can be passed to the mARGOt autotuner for further optimization at runtime.

For nodes with reconfigurable hardware, the compiler middle-end can produce different interfaces and descriptors for the hardware generation part (*HW and HLS* in Figure 1). From the Rust backend of the dataflow language, LLVM IR can be generated for the Bambu HLS tool. For the HPC kernels, the compiler can interface directly via MLIR or LLVM with Bambu, or generate C/C++ code with HLS pragmas for Vitis/Vivado or Bambu. Bambu's polyhedral analysis seamlessly interoperates with the representations used in the middle end. Custom number representations supported by the language for HPC kernels are compatible with those supported for Bambu for trade-off analysis (area, performance and accuracy). Information about lifetime of variables, data formats and data allocation (cf. Deliverable D3.1) can also be exported for custom memory subsystem generation using Mnemosyne. Mnemosyne then creates private local memories and the logic to bring the data to and from the right accelerator. Machine learning applications are processed within the Dosa framework. The Dosa framework intelligently selects the best implementation for the operators used in the deep neural network. After this phase, multiple different Register Transfer Level (RTL) implementations for standalone kernels, functions (nodes in the dataflow graph) or machine learning operators are generated via HLS using either Bambu or Vivado/Vitis.

The final phase of the compilation framework (code-gen and system generation in Figure 1 is responsible for creating the entire system on the FPGA(s), performing the HW-SW integration and finally generating the binaries and bitstreams. At this level, Olympus performs several optimizations to effectively use the area in the FPGA and balance the computation and communication time (specially relevant for systems with multiple memory channels). This phase can profit from a further MLIR integration in the second half of the project. In this way, operator scheduling and graph pipelining information from the upper compilation stages can be passed to the system integration.

# 3 Language Support and Intermediate Representations

This section discusses the language support (Section 3.1) and intermediate representations (Section 3.2 of the compiler framework. As specified in the project plan and Deliverable D4.1, we provide support for kernels in HPC and machine learning as well as for tasks and dataflow graphs. We had originally planned to support particle-based simulations in the compilation framework, but an explicit need was not identified in the requirement analysis (cf. Deliverable D2.2).

## 3.1 Language Support

## 3.1.1 CFDlang Extensions

Our starting point for the EVEREST kernel DSL was the CFDlang language [20], originally designed for CFD applications with primitives extended to cross-domain tensor expressions in [24]. It adopts an operator-based syntax for tensor expressions, as opposed to index-based expressions in languages such as TensorComprehensions [31]. This provides the freedom needed to implement data management techniques as described in Deliverable D3.1. Various extensions have been made to the implementation of this language in order to bring the EVEREST technology to the Inverse Helmholtz kernel use case. See Figure 2 for our driving inverse Helmholtz operator example in current DSL syntax.

At present, most extensions to CFDlang are related to the compiler implementation, and will be described in Section 3.2. This allows us to make major adjustments to the language itself very quickly, which was one of the prerequisites to achieve the use-case provider-centric design evolution targeted in Deliverable D2.2. We are currently at a point in language design where the application requirements have been identified and concrete implementations have been planned, but there is no coherent solution for all use cases yet. In this prototype phase, we have identified a few inconsistencies in the language and began to improve the integration into the EVEREST flow. For example, this includes changes to the way declarations are made, so that the DSL reflects the user's view of the application better, and forms a closer link to the EVEREST runtime (discussed later in Section 6).

```

var input S : [11 11]

var input D : [11 11 11]

var input u : [11 11 11]

var output v : [11 11 11]

var t : [11 11 11]

var r : [11 11 11]

t = S#S#S#u . [[1 6][3 7][5 8]]

r = D * t

v = S#S#S#r . [[0 6][2 7][4 8]]

```

Figure 2 – The inverse Helmholtz operator kernel in CFDlang DSL.

Future extensions will be necessary to achieve the targets set for the DSL in Deliverable D2.2 in a transparent and transferable fashion. Our current changes to the EVEREST kernel DSL and it's design include:

- Index-based expressions: While the absence of index-based expressions makes CFDlang free of Undefined Behavior (UB), we will relax this constraint to provide better support for use cases. In particular, a restricted introduction of implicitly ranged indices will allow mapping a larger subset of linear algebra, without introducing UB, while achieving a more readable syntax at the same time.

- Stencil application: Stencils are an important part of many numerical physics simulations, and are often prime candidates for the kind of optimization we pursue. With our interoperable pipeline based on MLIR, we now include language features that we can delegated to third-party components. With the Open-EarthCompiler [13], stencils are a logical first step in that direction, as they can also be of use to the exemplary EVEREST applications.

- Annotations: Although a maximum degree of automation is desired, it is still prudent to allow for external

D4.2 Intermediate report of the compilation framework

guidance through DSL annotations. As a first step, this gives us the tools to test and design more of our internal annotations that are used in the lowering process. For example, annotations that clarify intent and extra functional requirements, such as quantization information, give useful insight to the compiler that only the domain expert could provide.

## 3.1.2 Fortran Integration for WRF

One part of unifying the view the runtime and the user have on the application through the DSL is the method with which it is integrated into the existing codebase. In case of WRF, we have a large legacy codebase which makes a DSL integration particularly challenging. These challenges affect the EVEREST kernel DSL itself, its runtime library, and the "host application" (i.e. WRF in this case).

Our efforts have been three-fold in this regard:

• Fortran-style DSL syntax extensions: We rely on domain experts for the extraction of kernels from the host application. For domains such as weather modeling, this is a sensible approach, since they have lots of experience running simulations. In practice, this does not just mean identifying kernels, but also refactoring the legacy codebase to extract kernel invocations to function calls, so that we may provide an Foreign Function Interface (FFI) interface. In the case of WRF, this is relatively easy because of its inherent disaggregation of the individual driver components, but still requires the user to reason about the Fortran interface with all its peculiarities. By offering a new, optional declaration syntax, we accept a subset of Fortran that is relevant for FFI as shown below. As a result, the compiler can automate the error-prone process of matching the data layouts and transcribing the interfaces.

```

REAL :: S(11,11)

REAL, DIMENSION(11,11,11) :: D,u,v,t,r

```

C++-Fortran interop runtime library: The unification of the EVEREST flows has highlighted the need

for common interface abstraction. Towards such a unification, we started developing a common utility

library using the memref abstraction of the MLIR as the most general form of argument passing between

components.

A C++-Fortran interop library is also added to the EVEREST kernel DSL runtime (see Interop Layer in Section 6). In the short term, this library assists us in porting the Rapid Radiative Transfer Model for GCM Solvers (RRTMG) driver from its original source, especially when it comes to its integrating testing suite.

Pre-processing facilities: As a final method of reducing the barrier between DSL and host application, we added pre-processing facilities to our flow. With this scheme, we enable a mixed-source approach for applications like WRF, where the EVEREST kernel DSL can be merged with the original codebase. With regards to long term motivations for projects like ours, we consider it important to enable the application developers (in this context not the users but developers of WRF) to ship a compatible upgrade, even if our DSL can not yet reach that level of interchangeability.

#### 3.1.3 Dataflow

As basis for a language that can express dataflow, we use the Ohua compiler framework [8, 6]. An earlier prototype of the framework used its own frontend DSL that closely resembled the host language, but differed in the supported language features and the grammar definition [33]. The new version of the framework, instead, uses a subset of the host language as input. This allows the easy reuse of existing code, which significantly improves the usability of Ohua, one of the key requirements defined in Deliverable D2.2. More importantly, it also allows for quicker extensions of the compiler to support new languages as we can use existing parser and Abstract Syntax Tree (AST) definitions in both the front-end for parsing and the back-end for code generation. Ohua's middle-end is target-agnostic, which means that changes to the core logic of the compiler are usually not necessary to support a new language. Currently, front- and backends are implemented for both Rust and Python, albeit support for the latter is only experimental at the moment. In the following, we will focus on the

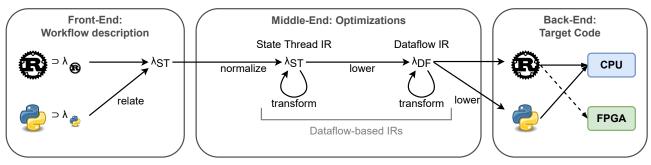

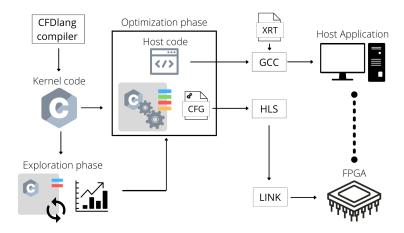

Figure 3 - Current status of the Ohua compilation flow.

Rust integration of our compiler, which is of higher relevance for EVEREST use cases. Figure 3 shows the current flow of the Ohua compiler. The end-to-end flow is explained in more detail in Section 3.2.3.

At its core, an Ohua algorithm (implemented in any supported language subset) is merely a composition of calls to both stateless and stateful functions in a separate file. The definition of such functions is not part of the programming model, i.e., they are not part of Ohua's compilation process. This allows for reuse of existing functions that implement the actual functionality of a program as well as operations on data structures, often referred to as methods. Developers provide a file of valid Rust code to the compiler, which will then in turn produce a file describing the same algorithm in parallel Rust.

An implementation of the *Probabilistic Time Dependant Routing* algorithm from the Traffic Simulation Use Case, would then look like this:

```

pub fn delay_profile(

route: Arc<Route<String>>,

2

departure_time: DateTime<Utc>,

prob_profile: Arc<SegmentsHistoryProbProfile<String, Quartiles>>,

samples: usize,

) -> Vec<Duration> {

let no_limit = Arc::new(NoLimitProbProfile::new());

let free_flow_duration = drive(route.clone(), departure_time, no_limit);

let mut res = Vec::new();

10

for _ in helpers::sample_range(samples) {

11

let duration = drive(route.clone(), departure_time, prob_profile.clone());

12

let delta = duration - free_flow_duration;

13

14

res.push(delta);

15

16

}

17

res

18

19

}

```

Deliverable D4.3 details how we arrive at this snippet by transforming the original code base.

In the middle-end, the Ohua compiler operates on a Dataflow Graph (DFG). This directly results in two fundamental restrictions on the input code:

• Using references is prohibited: In an Ohua program, each function call in the algorithm definition is regarded a single node in the DFG. After applying transformations to the graph, as outlined in Section 4.2, the resulting graph is serialized into Rust code. The parallel Rust code encapsulates each node of the graph by spawning it as a separate thread, realizing communication between these operators by using unbounded FIFO queues. This enables pipeline parallelism in the graph. But at the same time, this also means that using shared references becomes impossible. A simple solution to this problem is the introduction of reference counted pointers which allow the sharing of data across nodes at a negligible cost. We are looking into methods of automatically wrapping data structures in such pointers where

necessary, e.g., by enhancing the type checker along the lines of stacked borrows [14].

• Stricter move semantics: In a typical Rust program, primitive types and also some slightly more complex ones implement the Copy trait. This trait relaxes the strict ownership semantics of Rust by ad-hoc copying data on the fly when it is used several times in an owned fashion. While purely a quality-of-life improvement, copy semantics help to reduce bloat in the code by repeatedly having to clone data or using references as layer of indirection. Ohua is currently unable to support this feature because values generated during the execution of the algorithm are only visible in the scope of the dataflow node. Therefore, copying the result to multiple other nodes is impossible without a deeper understanding of the target language's type system, which is beyond the scope of our compiler implementation. As a result, developers need to resort to manually cloning any value produced during execution of the algorithm. Arguments to the algorithm are not affected by this and still support copy semantics, as the value can simply be copied into the different dataflow node scopes.

Other limitations such as the absence of support for if clauses mainly stem from the prototype nature of the compiler.

A key motivation behind using a dataflow-driven DSL in the EVEREST project is that a DFG abstracts over the individual computations that form the algorithm. This comes in handy when deploying such a program onto heterogeneous architectures. The abstraction will allow for a tight integraton for off-loading single nodes of the DFG to FPGAs using HLS, as outlined in Section 5.1. Since the off-loaded functions themselves are not part of the compilation process of Ohua, the main difference between offloaded functions and normal functions is the communication with the nodes. While normal nodes of the DFG communicate with one another using Rust's standard FIFO queues, communication with an off-loaded node requires actual data transfers from and to the accelerator. To notify the Ohua Compiler (ohuac) of this change, functions that will be deployed onto the FPGA will be annotated with a macro:

```

#[kernel]

let result = offloaded_computation(/* args */);

```

#### 3.1.4 Machine Learning

ML is a very active field of research, which gave birth to plenty of tools, standards, and frameworks aiming to support users and researchers. The EVEREST project decided to use the community-standard Open Neural Network eXchange (ONNX) as input language, which will be introduced briefly in the following.

The ONNX project [27] aims to enhance the interoperability of ML tools by developing a standardised format to export and import neuronal networks. ONNX is actively developed by a large community, managed by the Linux Foundation. ONNX defines a dataflow computation graph [29], together with built-in operators [28] and data types. Each node in this acyclic graph can have multiple in- and outputs and represents a call to an operator. ONNX is extensible, so that custom operators and data types can be used. The ONNX graph can be exported to .onnx files, which are compressed using Protocol Buffers [11]. Thanks to efforts on the ONNX-MLIR integration by the open source community (cf. Figure 1), supporting ONNX contributes to the convergence efforts of the EVEREST project.

An example of a decompressed graph containing a single 2D convolution with activation and pooling layers represented in ONNX is shown in Listing 1. The shown example is developed and trained in the tool Pytorch and exported via ONNX. Similarly, a user of the EVEREST ONNX flow would develop and train a neuronal network in her/his preferred tool and export it into the interoperable community standard ONNX.

# 3.2 Intermediate Representations

Our previous definition of the compilation framework had not mandated the use of a particular Intermediate Representation (IR), aside from the interface to Bambu. Still, we expressed our desire for a unified IR that, similar to embedded DSLs, combines both host and device code in a single place. With this alpha release, we

```

graph {

node {

input: "input.1"

input: "conv1.weight"

input: "conv1.bias"

output: "Conv_0"

op_type: "Conv"

attribute {

name: "dilations"

ints: 1

ints: 1

type: INTS

type: INTS

attribute {

name: "group"

i: 1

type: INT

}

attribute {

name: "kernel_shape"

ints: 5

ints: 5

type: INTS

}

attribute {

name: "pads"

ints: 0

ints: 0

ints: 0

ints: 0

ints: 0

}

}

attribute {

name: "strides"

ints: 1

ints: 1

type: INTS

}

node {

ode {

input: "5"

output: "6"

name: "Relu_1"

op_type: "Relu"

}

node {

input: "6"

output: "7"

output: "7"

op_type: "MaxPool_2"

op_type: "MaxPool"

attribute {

name: "kernel_shape"

ints: 4

type: INTS

}

attribute {

ttribute {

name: "pads"

ints: 0

ints: 0

ints: 0

ints: 0

type: INTS

}

attribute {

name: "strides"

ints: 4

ints: 4

type: INTS

}

node {

ode {

input: "7"

output: "8"

name: "Flatten_3"

op_type: "Flatten"

attribute {

name: "axis"

i: 1

type: INT

type: INT

}

}

node {

input: "8"

input: "fcl.weight"

input: "fcl.bias"

output: "9"

name: "Gemm_4"

name: "Gemm_4"

op_type: "Gemm"

attribute {

name: "alpha"

f: 1.0

type: FLOAT

}

attribute {

name: "beta"

f: 1.0

type: FLOAT

attribute {

name: "transB"

i: 1

type: INT

}

```

```

name: "torch-jit-export"

initializer {

dims: 36

dims: 3

dims: 5

dims: 5

data_type: 1

name: "conv1.weight"

raw_data: "..."

}

}

initializer {

dims: 36

data_type: 1

name: "conv1.bias"

raw_data: "..."

initializer {

dims: 10

dims: 1764

data_type: 1

name: "fc1.weight"

raw_data: "..."

initializer {

dims: 10

data_type: 1

name: "fc1.bias"

raw_data: "...

shape { dim {

dim_value: 1

dim_value: 3

dim {

dim_value: 32

dim {

dim_value: 32

}

}

}

}

output {

name: "8"

type {

tensor_type {

elem_type: 1

shape { dim {

dim_value: 1

dim {

dim_value: 1764

}

}

```

Listing 1 – A 5x5 Convolution with 3 in channels and 36 out channels followed by a Relu activation, a 2x2 max pooling, a batch flatten and one dense operation. The raw data of the weights and bias are omitted.

have begun embracing the MLIR as the single representation from front-end to system integration, wherever possible. We demonstrate the advantages of this approach in light of arbitrary precision floating-point computations and our now closely integrated Bambu flow. A unified IR promises interdependent optimization of host and device code, which is key to our planned system integration flow, carrying over our previous achievements.

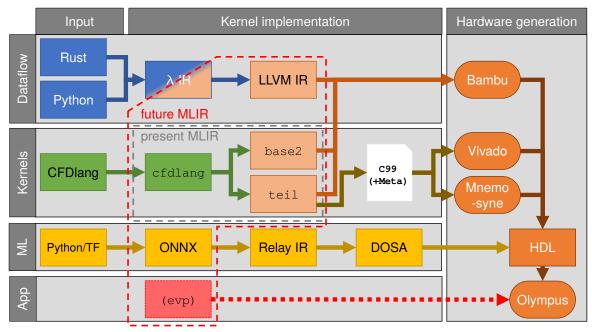

Figure 4 - Overview of current and planned IR collaboration.

Figure 4 shows a collaboration diagram of the different IRs currently used, and the currently planned changes. Depicted is a subview of Figure 1, which starts from the input languages and ends at the system integration level. The three application flows are separated by their front-ends, which we expect to be able to merge with little effort, using existing MLIR infrastructure and our extensions to it. While the contrast in the application domains makes interoperation between middle-end components not very likely, we are still looking to share an MLIR representation here in multiple places. This is especially relevant for the planned extensions to the way Olympus will integrate with applications, for which we imagine a unified application-embedded support runtime with a custom MLIR dialect (indicated by evp in Figure 4).

Components which are currently precluded from a fully integrated MLIR infrastructure are our machine learning and dataflow-centric flows. However, we do not view this as problematic, since interoperability can be achieved with currently available third-party components. In addition, we expect future developments in the field of MLIR front-ends to widen the range of supported programs and languages considerably.

#### 3.2.1 Design Rationale

Extending MLIR for a new kind of language, application domain or target device is made easy through its decoupled dialect infrastructure. We are able to develop the DSLs, the runtime and the device drivers mostly independently, and represent them as independent parts within the same IR. A unified flow through MLIR is also eased by its ability to interact with third-party components, which can provide further domain-centric optimizations or languages.

The key aspects of this design are:

Front-end integration: By connecting the DSL front-end directly within MLIR, we greatly speed up the

iterative language design process we are facing. Additionally, we provide tangible benefits to the user of

our EVEREST SDK. Through the use of MLIR's facilities and location tracking, we can provide accurate

debug information and relate implementation obstacles back to DSL code. Not only does the domain

expert receive more valuable error information and performance hints, our dialect design also allows a

backward flow that can visualize changes to them as DSL code.

- Separated domain-centric optimizations: To enable truly cross-domain capable optimizations, we must

clearly separate them from the front-end tasks related to host code embedding, and make them entirely

independent of target-specific transforms. MLIR provides a growing ecosystem of dialects that are designed for this purpose, and we extend it with new ones that fit into this existing hierarchy. We want to

give future users the power to plug their own components in these places, which is made possible by

MLIR.

- Abstract interfaces: A dependency from an abstract to a concrete dialect is often the easiest way to

introduce a new level into the hierarchy, but violates the single responsibility principle on a higher level.

We adopt a design where the higher level dialects only provide abstract definitions of e.g. number formats,

memory transfers and accelerator resources. This allows us to freely add implementing dialects, such as

new target devices, and gives them the highest degree of freedom possible.

We are still using components that are not native to MLIR, which means that interchange formats entering and leaving it are required (cf. Figure 1). For example, we projected that a C99-based transpiler would need to be employed for preparing HLS code. In the unified MLIR flow, we are providing a back-end translation that emits such C99 code, allowing us to interface with vendor tools. Similarly, ONNX can be round-tripped through MLIR using third-party projects, which allows us to plumb our machine learning flow more quickly to a unified front-end. MLIR is also capable of exporting to LLVM-IR, which can be reused by a variety of external tools with outstanding availability and capabilities.

Our new advancements in interfacing with Bambu have shown that MLIR can ultimately substitute all this, with added benefits on top. Bambu accepts LLVM-IR, the process of obtaining which is destructive to metadata we attach to MLIR, cutting Bambu off from any domain knowledge much like in the C99 case. However, Bambu provides its own MLIR input path, which can perform elaborate transformations on the information available there. We are now designing dialects to act as vendor interfaces to such functionality, which has already enabled arbitrary precision floating-point numbers for our numerical kernel flow.

#### 3.2.2 MLIR Language Stack for Numerical Computations

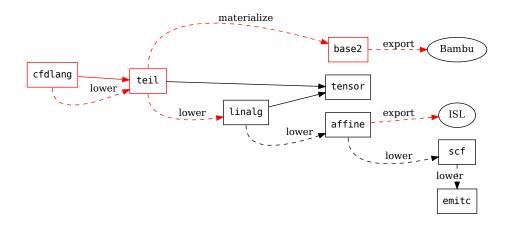

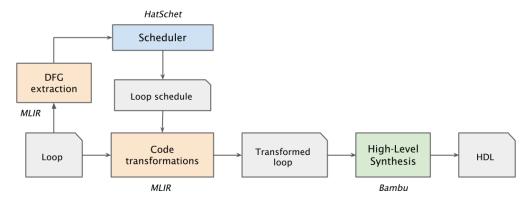

Our most tightly MLIR-integrated flow yet is the one for numerical kernels, which currently uses the CFDlang DSL as input. Following the guidelines from Section 3.2.1, we have implemented a set of dialects that implement the desired separation. Figure 5 shows the dialect hierarchy from abstract on the left to concrete on the right (following from the specification in Figure 8 of Deliverable D4.1). In this flow, cfdlang takes the role of the front-end dialect, which subsumed all the previous diverging AST and expression tree IRs. The teil dialect is our proposal for a cross-domain tensor expression optimization framework, and is implemented more conventionally with a direct dependency on the existing linalg dialect. It provides an abstract number representation interface, which allows an implementation dialect, such as our own base2 dialect, to implement tensor scalar types.

The compilation flow is depicted in Figure 6, which shows when these dialects are used. The teil dialect exists transiently as a means to perform our domain-centric optimizations, such as tensor factorization. Using the base2 dialect, the scalar type is then implemented, which continues to coexist with the rest of the program until it is passed to synthesis. After scalar type implementation, we enter the target-specific part of this flow, where teil can also be used effectively, but further steps are only downward in the dialect hierarchy. This proceeds until a synthesizable artifact is obtained, at which point MLIR is either exited towards a vendor tool, or passed to the Bambu input pipeline.

One advantage of this flow is that it directly enables us to target CPUs, and also puts GPUs in range of future extensions. As an example, Figure 7 shows the inverse helmholtz operator kernel in the cfdlang dialect in MLIR, next to an excerpt of its LLVM-IR lowering. This lowering is obtained using standard MLIR components directly from the bottom of our dialect hierarchy, and can be processed with LLVM optimizers for targeting a multitude of different CPU architectures.

Figure 5 – MLIR dialect dependencies for numerical computations. EVEREST additions marked in red.

Figure 6 – Dialects in the MLIR flow for numerical kernels.

```

module {

cfdlang.program {

cfdlang.program {

cfdlang.input @S : [11 11] cfdlang.input @D : [11 11 11] cfdlang.input @D : [11 11 11] cfdlang.input @D : [11 11 11] {

cfdlang.input @D : [11 11 11] {

cfdlang.offine @t : [11 11 11] {

cfdlang.offine @t : [11 11 11] {

cfdlang.offine @t : [11 11 11] {

cfdlang.eval @S : [11 11] {

cfdlang.eval [2 5] {

<td

```

```

; ModuleID = '<stdin > source_filename = "LL

"LLVMDialectModule"

@__constant_11x11x11x164 = private constant [11 x [11 x [11 x double ←→

]]] zeroinitializer

declare i8 * @malloc(i64)

declare void @free(i8*)

define void @kernel(double• %0, double• %1, i64 %2, i64 %3, i64 %4, ← i64 %5, i64 %6, double• %7, double• %8, i64 %9, i64 %10, i64 ← %11, i64 %12, i64 %13, i64 %14, i64 %15, double• %16, double• ← %17, i64 %18, i64 %19, i64 %20, i64 %21, i64 %21, i64 %23, i64 ← %24, double• %25, double• %26, i64 %27, i64 %28, i64 %29, i64 ← %30, i64 %31, i64 %32, i64 %33) { %35 = call dereferenceable_or_null(10648) i8• @malloc(i64 10648) %36 = bitcast i8• %35 to double• br label %37

; preds = %63, %34

%38 = phi i64 [ %64, %63 ], [ 0, %34 ]

%39 = icmp slt i64 %38, 11

br i1 %39, label %40, label %65

; preds = %37

41:

%42 = phi i64 [ %62, %61 ], [ 0, %40 ]

%43 = iomp slt i64 %42, 11

br i1 %43, label %44, label %63

: preds = \%61. \%40

44:

br label %45

; preds = %41

; preds = %48, %44

5:

%46 = phi i64 [ %60, %48 ], [ 0, %44 ]

%47 = icmp slt i64 %46, 11

br i1 %47, label %48, label %61

; preds = %45

%49 = mul i64 %38, 121

%50 = mul i64 %42, 11

%51 = add i64 %49, %50

%52 = add i64 %51, %46

```

Figure 7 – Example lowering from cfdlang to LLVM-IR (excerpt).

#### 3.2.3 Dataflow

The compilation process for heterogeneous dataflow applications involves two different types of intermediate representations. One is the internal representation of Ohua, which is used to reason about the dataflow within a program. The other IR is used to communicate with the kernel compilation phase.

## 3.2.3.1 Internal Dataflow Representation

The programming model promoted by Ohua with its restrictions on variable usage enable the compiler to easily translate an algorithm into a dataflow graph. This representation exposes pipeline and task-level parallelism while preserving the algorithm semantics. And while the actual internal representation in the compiler consists of several stages exposing different key aspects of the graph more clearly, as explained in Deliverable D4.1, this generalized view suffices to explain the core concepts of the compiler.

Ohua first translates the sequential input algorithm into applicative normal form and afterwards transforms it from an imperative into a functional form. This transformation relies on the notion of state threads which we already explored earlier [7]. Every call to a stateful function there becomes a state thread which accepts a piece of state as input, mutates it, and yields the modified state again. Similarly, a call to a stateful function within a loop turns the whole loop into a state thread.

From this functional description, Ohua translates stateful and stateless function calls into nodes of a dataflow graph. Data dependencies between nodes are transformed into arcs that transfer data values in FIFO order. The different types of nodes in our dataflow graph are denoted as follows:

The first two node types execute calls to stateless and stateful functions respectively. In order to perform a call, a node needs to retrieve a data value from each of its incoming arcs and emits the result of the call to its outgoing arc before the next call is constructed. Stateful nodes additionally emit their updated state via a dedicated outgoing arc. Ohua translates loops and tail recursions directly into dedicated dataflow nodes. The for node streams the elements of the vector into its outgoing arc. The trfix node models the concept of tail recursion in the graph. Both language constructs, loops and tail recursion, open a new contextual scope, i.e., a subgraph. For tail recursion, this subgraph is closed such that the only way for data to enter and leave the graph is the trfix node. For loops, data enters the subgraph via for and reuse nodes and leaves it via a stateful function call node. Data that enters the loop subgraph via the for node "drives" the computation. reuse nodes gate the arcs that receive the data entering the loop. It attaches a reuse count n where n is the number of loop iterations, i.e., elements in the looped vector. Function call nodes that receive such a data value reuse it over the course of n calls.

This internal representation is generic, which means that it is shared by all language integrations. However, the back-end of the compiler may require certain information from the original input code, such as data type annotations in the case of the Rust integration. To facilitate this, the intermediate representation of the middle-end is designed to encapsulate such information and allow its transfer into back-end code generation.

## 3.2.3.2 IR for Kernel Compilation

The use cases that we have already explored with Ohua in the EVEREST project are written in Rust. However, the kernel compilation flow invoked via Bambu is unable to work with this language. Therefore, we are using LLVM IR as interfacing layer between both tools, as the Rust compiler builds on top of LLVM and is therefore natively able to emit this IR. With this glue layer in place, ohuac does not have to touch the code to be off-loaded, as it is directly fed to rustc. Nonetheless, the function in question needs to be annotated with the #[no\_mangle] macro to allow Bambu to actually find this specific piece of code. Additionally, a few restrictions are placed on the LLVM IR to be generated by rustc:

- No panic unwinding When a Rust program encounters an unrecoverable error, a panic is triggered, which normally results in the executing thread being halted and the stack being unwound, calling destructors for all data types. This behavior needs to be disabled. Instead, a program must abort on a panic.

- No overflow checks rustc adds a number of overflow checks to the code to provide more safety at runtime. This functionality is not required when off-loading the code to an accelerator.

- No loop vectorization and Superword Level Parallelism (SLP) Since Bambu will transform the input code itself, it makes no sense to run performance optimizations like vectorizations beforehand.

As mentioned before, future work will be aimed towards moving to a fully integrated MLIR infrastructure where this flow may also emit kernel specification code in this unified IR.

#### 3.2.4 Machine Learning

The EVEREST project decided to use another machine-learning community framework, TVM [26, 4], for high-level optimizations and to reuse it's IR, RelayIR [21]. RelayIR is a functional intermediate representation for ML tasks, developed by the TVM community and based on HalideIR [19] and we decided to use RelayIR within EVEREST due to several considerations: First, TVM has an active community around Deep Neuronal Networks (DNN), it is actively developed, and has connections to the FPGAs community [16]. Second, a being a functional language, Relay is well suited to be hardware and platform agnostic. Third, TVM contains already a lot optimization passes for Relay IR and finally, Relay IR is able to also represent the training phase of DNNs. For further discussions around the usage of TVM within EVEREST, we refer the reader to Section 3.3 of Deliverable D4.1.

After importing the network description via an ONNX file, the network is converted into a RelayIR module and subsequently optimized using built-in optimization passes, such as constant folding or operator fusion. The optimized RelayIR module of the ONNX representation in Listing 1 is shown in Listing 2.

```

def @main(%input.1: Tensor[(1, 3, 32, 32), float32]) → Tensor[(1, 10), float32] {

%3 = fn (%p03: Tensor[(1, 3, 32, 32), float32], %p11: Tensor[(36, 3, 5, 5), float32], %p21: Tensor[(36), float32], Primitive=1) → Tensor[(1, 36, 28, 28), ← float32] {

%1 = nn.conv2d(%p03, %p11, Tensor[(1, 3, 32, 32), float32], Tensor[(36, 3, 5, 5), float32], padding=[0, 0, 0, 0], channels=36, kernel_size=[5, 5]) /* ty=← Tensor[(1, 36, 28, 28), float32] */;

%2 = nn.bias_add(%1, %p21, Tensor[(1, 36, 28, 28), float32], Tensor[(36), float32]) /* ty=Tensor[(1, 36, 28, 28), float32] */;

nn.relu(%2, Tensor[(1, 36, 28, 28), float32]) /* ty=Tensor[(1, 36, 28, 28), float32] */;

%1 = %3(%input.1, meta[relay.Constant][0] /* ty=Tensor[(36, 3, 5, 5), float32] */, meta[relay.Constant][1] /* ty=Tensor[(36), float32] */) /* ty=Tensor[(1, 46, 28, 28), float32] */;

%5 = fn (%p02: Tensor[(1, 36, 28, 28), float32], Primitive=1) → Tensor[(1, 36, 7, 7), float32] {

nn.max_pool2d(%p02, Tensor[(1, 36, 28, 28), float32], */;

%7 = fn (%p01: Tensor[(1, 36, 7, 7), float32] */;

%7 = fn (%p01: Tensor[(1, 36, 7, 7), float32] */;

%8 = %7(%d) /* ty=Tensor[(1, 36, 7, 7), float32] */;

%8 = %7(%f) /* ty=Tensor[(1, 164), float32] */;

%9 = fn (%p01: Tensor[(1, 164), float32] */;

%9 = fn (%p02: Tensor[(1, 1764), float32], fensor

```

Listing 2 – Optimized RelayIR with type annotations of Convolution example shown in Listing 1.

The RelayIR module is extended by additional annotations in order to be useful for FPGA architecture generation within the EVEREST ML tool chain, called Dosa. The first important annotation consists of performance characteristics for each (fused) operation. Using the type annotations of RelayIR a custom Relay pass calculates the Operational Intensity (OI) of each operation. The OI is calculated in two versions: One is calculated taking the parameters and the input data into account, the second is calculated with just the input data. These two different OIs are used for architectural decisions later. The OIs for function %3 of the example in Listing 2 would be:

- OI of function %3 for data+parameters: 181.02

- OI of function %3 for just data: 342.24

The second important type of annotations are implementation options. After optimizations of the AST and the performance annotations are done, each operation gets annotated with a list of it's implementation possibilities. This implementation options refer to HLS or Hardware Description Language (HDL) libraries that are re-used by Dosa and could implement this particular operation. Further details for this approach are explained in Section 4.3.

# 4 High-Level Transformations and DSE

This section describes how the compiler framework leverages the IRs described in Section 3.2. The section starts by describing the optimizations that the framework includes at the kernel level (Section 4.1), including a prototype of the multi-variant generation flow. The dataflow transformations for performance and to enable seamless offloading to accelerators are described in Section 4.2. Section 4.3 describes the transformations applied to ML workloads. This section closes with general remarks on the code generation flow after the middle end in Section 6.

## 4.1 Kernel Transformations and Optimizations

Using the MLIR infrastructure, we have implemented / have access to a set of kernel transformations applicable to our higher abstraction levels.

- Expression canonicalization: MLIR supports a canonicalization mechanism that repeatedly applies a set of rewrite rules until a fixpoint is reached. In our abstract cfdlang and teil dialects, we use this extensively to simplify the kernel programs. As a result of using abstract number types, this allows us to reason about expression equality for all our DSL's statements.

- Tensor expression rewriting: The teil dialect was designed with implicit tensor elements in mind such that algebraic identities could be exploited easily. Our tensor expression rewrite patterns make use of this, reducing the time complexity by exploiting, e.g., associativity and distributivity. Aside from algebraic transformations, such as factorization of tensor contractions, we support platform-specific implementation choices. In an approach similar to [22], we can use tensor rewrites to establish different forms that map to specific hardware, such as systolic arrays or Single Instruction Multiple Data (SIMD) execution units. Currently, we can rewrite contractions into TTGT [15] for use with accelerators that offer efficient general matrix-matrix multiply (GEMM) implementations.

- Operator scheduling: For efficient implementation on FPGA devices, careful consideration of the memory architecture is needed. A first step is to optimize streams for the available throughput of the system memory banks, which is especially important for our High Bandwidth Memory (HBM) targets. In MLIR, we can establish the required pipeline structure on a high abstraction level before proceeding to subkernel implementation.

- Scalar type implementation: Since cfdlang and teil use abstract scalar types, we defer the concrete

implementation to target-aware lowerings. We plan on adding quantization hints to cfdlang, which will be

used in teil to guide the placement of precision boundaries. Currently, these are placed explicitly, and

are then lowered onto synthesizable target types using the base2 dialect.

- Bufferization: Another part of memory optimization is the size, layout and lifetime of buffers for intermediary results. We currently rely on MLIR's built-in reasoning, extended by our previous efforts to reduce buffer usage through after-scheduling sharing. We plan to merge these steps into one, potentially inside MLIR, allowing more back-end flows to make use of these optimizations.

Outside of MLIR, we support a Mnemosyne-enabled flow (cf. Section 5.2) powered by in-MLIR kernel analyses exported from our compiler. In addition, we use our new MLIR infrastructure to facilitate MLIR-to-DSL conversions, which provide interactive feedback to the domain expert. An example of this was also featured in our 4th webinar, and is also included in Deliverable D4.3.

Our current method for guided HLS still relies on low-level abstraction IRs, such as polyhedral descriptions in the affine dialect. During our higher level MLIR transforms, we can establish resource estimates in terms of memory bandwidth. On the polyhedral level, we use this to reschedule sub-kernel regions for HLS, inserting annotations. This means that we output vendor-specific pragmas, such as Xilinx's #pragma HLS <?>, into an interchange format, such as C99. Flows with better MLIR integration, such as Bambu, remove the interchange

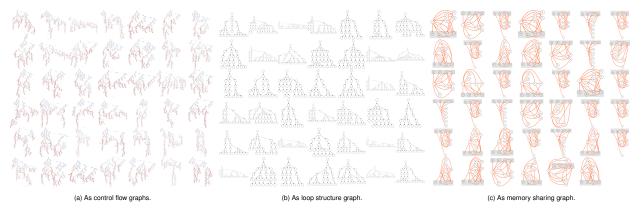

Figure 8 – Different implementation variants of the kernel in Figure 2. Each cell in a matrix is a variant, with cells at the same location corresponding to the same variant.

format in favor of passing this information directly in MLIR. We are working towards further improving these capabilities.

We perform DSE at two different abstraction levels. The first is the selection of alternative formulations in expression rewriting, such as systolic arrays, and the second is during the HLS lowering step. In this last step, polyhedral scheduling alone introduces a huge flexibility in terms of possible implementation, as illustrated by Figure 8. In addition to software enabled variance through tunable hyperparameters, this adds a dimension of hardware kernel variants that need to be ahead-of-time compiled.

In Deliverable D5.1, we present mARGOt as a runtime autotuner to implement both scenarios. Currently, we have the ability to estimate performance indicators for the variants we are able to generate, and classify them, all within our IR. We plan on extending this classification to certain plausible runtime scenarios, i.e. conditions under which the optimal trade-off between resources, accuracy, performance and other varying properties changes. We will include a set of variants for each of these classes into the compiled artifact, which mARGOt is then capable of selecting from at runtime. For instance, in our simplest demonstration scenario, this includes providing a variant for each target (e.g. CPU + bus attached FPGA + cFPGA), selecting based on availability.

# 4.2 Dataflow Transformations and Optimizations

Ohua conducts a number of dataflow transformations that have been outlined in Deliverable D4.1 already. These are mainly concerned with improving performance of the algorithm independently of the target architecture. Additionally, some transformations are necessary to nodes that are to be deployed to an FPGA.

#### 4.2.1 Performance-Related Transformations

Naturally, a dataflow graph exposes task-level parallelism (nodes with no data dependencies between one another may execute in parallel) and pipeline parallelism. The first and perhaps simplest transformation therefore is to also enable data parallelism. Data parallelism arises from an implicit (in-)dependence between the same stateless function call across loop iterations. As such, every stateless function call inside a loop is an opportunity for data parallelism, but introducing data parallelism into a static dataflow graph as shown in Figure 9a leads to suboptimal performance. This is due to the assumption that all n nodes  $f_{\rm SL}^1 \dots f_{\rm SL}^n$  perform exactly the same computation which is often not the case. Instead, inputs often dictate how long a function will run. As such the deterministic merge in the collect node stalls waiting for straggling work [12].

To mitigate this effect without sacrificing determinism, we integrate dynamic dataflow into our static dataflow graph. In a dynamic dataflow graph, nodes are created at runtime. A node is a task such as executing a stateless function call that gets <code>spawned(/forked)</code> on demand and executes once. Spawning a task creates a handle to its <code>future value</code>, i.e., the result of the stateless functionc call. This handle provides a <code>get</code> method to <code>join</code> the forked and the current task by blocking until the call completed and the result is available. Tasks are

Figure 9 - Static vs. dynamic data parallelism in the dataflow graph.

processed by a pool of threads. Whenever a thread is idling, it may steal tasks from other threads to reduce idle time. In case of the PTDR algorithm, a thread that already finished its delay computation may steal queued computations from a thread with a long-running delay computation.

The transformation in Figure 9b integrates dynamic dataflow to data-parallelize nodes with stateless function calls and uses the static dataflow to preserve the data value order, i.e, determinism and the semantics of the algorithm. Instead of replicating the stateless function call  $f_{\rm SL}$  node, we lift it into a spawn< $f_{\rm SL}$ > node. For every received input, when normally a stateless function call would be executed, the spawn< $f_{\rm SL}$ > node submits this computation as a task to a work-stealing runtime system and emits corresponding *future*. The downstream get node retrieves the value from the future. No reordering takes place because both spawn< $f_{\rm SL}$ > and get are stateless function call nodes in the static datalfow graph connected via a FIFO channel.

When applications evolve around manipulating a large piece of shared state, they are called *irregular*. Parallelizing such computations often yields *amorphous data parallelism*. This means that the order in which elements from the input worklist are processed will dictate, how the remaining elements will be processed and whether new work elements may be created by processing an element. Hence, updates of the data structure not only depend on the input data, but also on the current state of the data structure itself. This direct loop-carried dependency means that parallelizing a loop operating on such a piece of state may not be parallelized in a straightforward manner. Existing approaches such as Software Transactional Memory allow the parallelization of these loops by wrapping them in transactions: Small code blocks which detect conflicting accesses to shared state and issue recomputations where necessary. However, these conflicts are an implicit side-effect that can significantly impact performance.

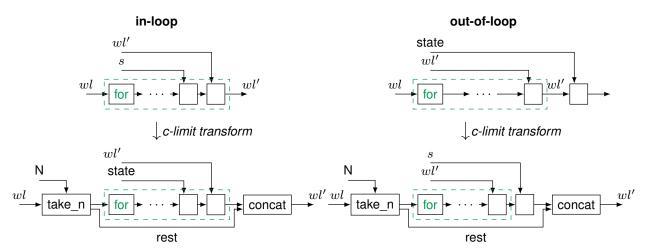

We provide a data parallelism transformation that makes these implicit effects explicit in the dataflow graph and exposes a knob to fine-tune runtime performance. The transformation targets irregular algorithms that (tail-)recurse over a worklist wl to evolve a complex data structure, i.e., a state s. We distinguish between two patterns: One, where the update to the state s happens inside of a loop and one where the state update happens after the loop has completed. The idea of this transformation is to limit the number of possible conflicts by running only a small number of computations from the worklist in parallel before updating the state. This ensures that the state is updated more frequently and following computations run on the updated state. Doing so exposes an inherent trade-off because smaller batch sizes lead to more iterations, which generate more overhead. At the same time, too big batch sizes lead to more conflicts, because more computations have been executed on the same state snapshot, leading to stale data that's no longer applicable. We depict our transformation that extracts amorphous data parallelism in Figure 10. In both cases, the take\_n-node extracts the first N data items from the worklist wl and concatenates the rest with the recomputations after the s was updated.

#### 4.2.2 Transformations for Offloaded Kernels

Since Ohua regards the functions that algorithms are composed of as black boxes anyway, offloading single functions onto a hardware accelerator only affects the generation of the wrapper around the node. Instead of actually calling the function associated with the node, the wrapper becomes shallow. It merely forwards any incoming data to the FPGA and pipes computation results back to the output arcs of the node.

It is also conceivable to split the node into two parts, where the first will transmit the input data to the accelerator while the second one receives the computation results. This would enable pipelining the data transmissions for a possibly small performance gain.

Figure 10 - Transformation for amorphous data parallelism

# 4.3 Machine Learning

Before describing the DSE that are applied to the imported RelayIR module of Section 3.2.4, we briefly elaborate on the motivation to do those transformations:

## 4.3.1 Engine and Streaming type of ML architectures

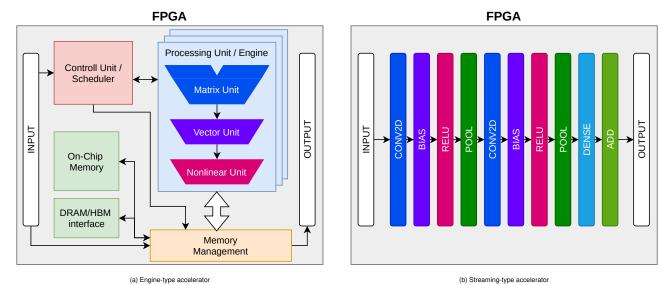

For over a decade, the FPGA community researches the acceleration potential of Al applications. The recent publicity and promotion of Al in the industry lead to a "Cambrian explosion"[9] of new architectures and products for accelerating DNNs on FPGAs, scaling from Edge to Cloud and for a wide variety of applications. Despite this variety, all existing frameworks can be sorted in two categories: **Engine-type** or **streaming-type** of acceleration (micro-)architectures, as depicted in Figure 11.

The first, engine-type, often also referred to as *NPU* or *xPU*, and shown in Figure 11a, consists of one or multiple custom designed processing units (i.e. engines) that can execute domain specific instructions. These processing engines often contain dedicated units for matrix multiplication, vector processing, and non-linear functions, since this are the mathematical foundations for today's DNNs. Consequently, a DNN is brokendown by a compiler into instructions that can be handled by those processing engines. These instructions are issued by a control unit at run-time and scheduled based on memory dependencies and processing unit availability. Although this pattern is simple, the design-space is huge: The processing elements can contain a variety of different specialized units, with different data sizes or types. In addition, the control unit and memory management can be either quite *stupid*, which means scheduling must mostly be decided by a compiler before run-time, or more intelligent with out-of-order execution or dynamic memory management. Examples for this type of acceleration architecture is TVM's VTA [16], Xilinx's Vitis AI [34], and Microsoft's Brainwave [9].

The second architecture template, the streaming-type, depicted in Figure 11b, bakes the application specific operations into the FPGA logic, so that at run-time the data *just* streams through the logic. This type of accelerator can achieve higher throughput with lower latencies, at the cost of a higher resource usage, compared to the engine-type. Despite this fixed principle, the design-space of this template is also huge: Starting with different data precision per operation to a large variety of loop-unrolling approaches. Example frameworks for this type of accelerators are hls4ml [5], Haddoc2 [1], or FINN [2].

#### 4.3.2 Leveraging Existing ML-tools for FPGAs

There are already a lot of DNN-to-FPGA tools available in public literature. Each of these tools solves a particular challenge in a good, thought-through and efficient way, so why not reuse these efforts of the community? For example, if a user needs a solution for low-latency inference with small kernels on Xilinx FPGAs, there is an

Figure 11 - Two major types of NN accelerator architectures (Based on [32]).

actively developed framework available (hls4ml [5]). For Intel FPGAs, the user may choose another framework with engine-type [3]. In another situation, if the user has to solve a problem that requires extreme throughput, but could maintain it's accuracy with binary weights, LogicNets would be a solution [30].

However, for choosing this options, the user must be aware of their existence and also the trade-offs between them. With Dosa, we try to provide a holistic DNN-to-FPGA solution by automatically taking these decisions, but without "re-inventing the wheel" by re-implementing already proven solutions from the research community. Hence, we try to re-use existing (third-party) open source frameworks as much as possible and Dosa will offload a particular problem to another tool, if it detects this tool can solve this particular problem efficiently for the desired target device.

Following this path, Dosa needs a hardware-agnostic application-independent unified description of the DNN to be able to decide to offload which part to which tool. We decided to use RelayIR, as justified in Section 3.2.4.

#### 4.3.3 DSE for ML Workload

Both architecture *templates*, streaming and engine, as discussed in the previous subsections are well justified for different reasons. The streaming template is best if used for smaller DNNs that require high-throughput and/or low latencies. Engine-type accelerators are better for larger DNNs, resource or cost constrained usecases, or latency-relaxed environments. To decide which architecture is best for a particular network, performance characteristics and the targeted performance are required.

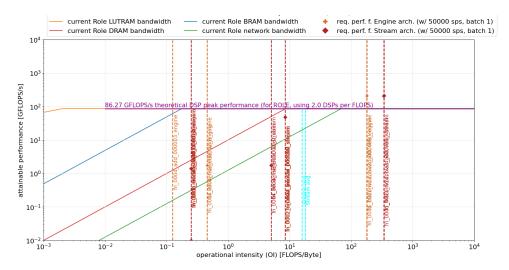

Alongside the input .onnx, the user of Dosa must provide *target constraints*, as also described in Deliverable D4.1. Those constraints state the resource budget, in terms of how many devices of which type are available, or the desired throughput in samples-per-second. After annotating the OI of each operation in the AST as described in Section 3.2.4, the required performance as well as bandwidth requirements are calculated for each operation and compared to the available bandwidth for a particular hardware. This analysis can best be visualized using a *Roofline* diagram, as shown in Figure 12. This analysis is performed for each operation twice: Once as streaming-type and once as engine-type, using the two types of OI annotations described in Section 3.2.4.

As can be seen in Figure 12, the OI for dense and convolution differs strongly for the different architecture templates, while max pool is indifferent. In this case, the dense operation in an engine-type accelerator would be heavily limited by the network or DRAM bandwidth, while the streaming-type accelerator would perform nearly optimal. In contrast to this, the difference of the OI of the two 2D-convolutions are with half-a-magnitude less significant and unimportant, since all versions are "only" compute-bound. But "baking-in" the two convolu-

Figure 12 - Per-operation roofline analysis of the example convolution of Listings 1 and 2.

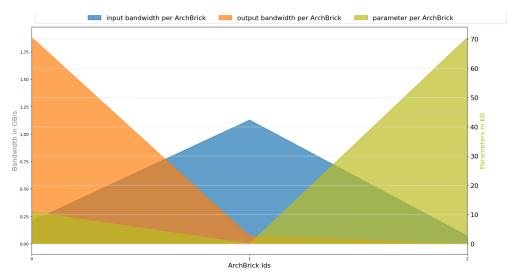

Figure 13 – Bandwidth and parameter requirements per operation for the example convolution of Listings 1 and 2. (ArchBrickId is roughly the layer number)

tions in the FPGA logic, would consume twice the resources than if both would use the same engine. Following this path, it would make sense to create an accelerator where the first layers are executed on an engine type and the dense layers at the end on a streaming architecture. This would achieve the same performance like an all-streaming approach, but would save resources. On the contrary, the required bandwidth for data between layers within a DNN tends to decrease throughout the network, as shown in Figure 13. Looking at this figure, one can get the opposite impression and could argue for a streaming-architecture in the beginning and engine-types in the end, to accommodate the high-bandwidth requirements of the first layers.

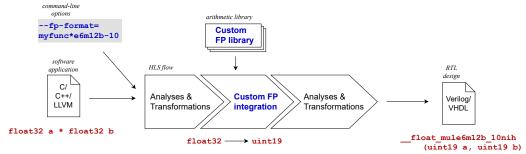

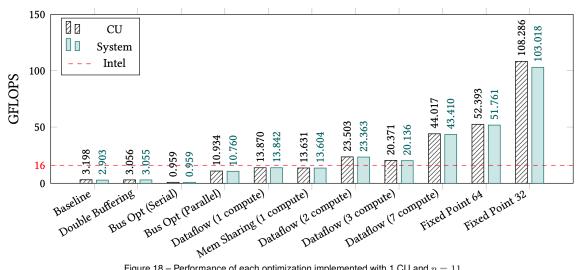

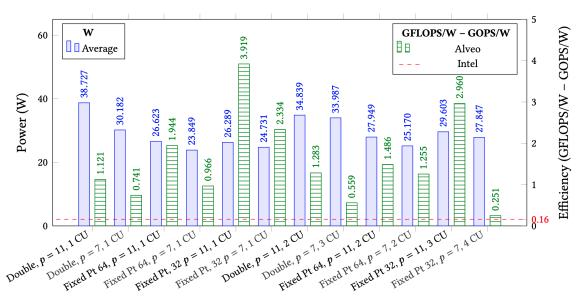

Both previous described proposals profit from the combination of streaming and engine templates. But which one is the "correct" or "better" one is only possible to tell after analyzing every operation of a given DNN, based on performance goals provided by the user. Based on this performance requirements, a compiler could decide if the engine-type accelerators in the beginning would be sufficient. Consequently, asking the user for performance targets, has two positive effects: First, it allows for a holistic analysis and DSE. And second, it enables early feedback to the user if the available hardware and architectures would meet this goals.